**Department of Physics and Astronomy**

**University of Heidelberg**

Master thesis

in Physics

submitted by

**Dieter Liebert**

born in Stuttgart

**2019**

# Test and Monitoring Procedure for the T<sub>R</sub>E<sub>X</sub> Module

This Master thesis has been carried out by Dieter Liebert

at the

Kirchhoff-Institute for Physics

under the supervision of

Prof. Dr. Hans-Christian Schultz-Coulon

### **Zusammenfassung:**

Um im Zuge der zukünftigen LHC-Upgrades weiterhin eine hohe Effizienz an Triggerentscheidungen zu gewährleisten, werden einzelne Module des ATLAS Level-1 Kalorimetertriggers ersetzt oder überarbeitet. Eine Erweiterung des Preprocessors dient dabei der optischen Bereitstellung von Tile-Kalorimeterdaten an die neuen Triggerprozessoren bei simultaner Datenübertragung zu den Altsystemen mittels LVDS. Die „Tile Rear Extension“(TREX) Leiterplatten sind dazu mit modernsten FPGAs und optischen Hochgeschwindigkeitssendern ausgestattet.

In dieser Arbeit werden TREX Prototypen zunächst bezüglich ihrer Betriebsbedingungen zur Einhaltung der einzelnen Bauteilspezifikationen und Abschätzung der Leistungsaufnahme unter größtmöglicher Last überwacht. Dies ergibt einen maximalen Verbrauch von 43 W. Weiterhin wird der Datenempfang in deren Hauptverarbeitungseinheit sichergestellt und einem Langzeittest unterzogen. Die Bewahrung der richtigen Strahlkreuzungszuweisung von Daten und deren zeitliche Ausrichtung wird aufgezeigt. Die optische Übertragung wird anhand von Augendiagrammen und standardisierten IEEE Anforderungen in eigenständigen Prüfschleifen und gemeinsamen Tests mit einem Zielprozessor charakterisiert. Dabei wurden Bitfehlerraten von  $1.7 \times 10^{-15}$  auf allen Übertragungsstrecken gemessen. Ein Latenzzeitenvergleich zum bisherigen Datenpfad zeigt keinen kritischen Zuwachs. Ein sicherer Betrieb des TREX-Moduls ist damit gewährleistet.

### **Abstract:**

In order to ensure a high efficiency of trigger decisions in the course of future LHC upgrades, individual modules of the ATLAS Level-1 Calorimeter Trigger will be replaced or revised. An extension of the Preprocessor serves for the optical provision of Tile calorimeter data to the new trigger processors with simultaneous data transfer to the legacy systems via LVDS. For this purpose, the "Tile Rear Extension"(TREX) PCBs are equipped with state-of-the-art FPGAs and high-speed optical transmitters.

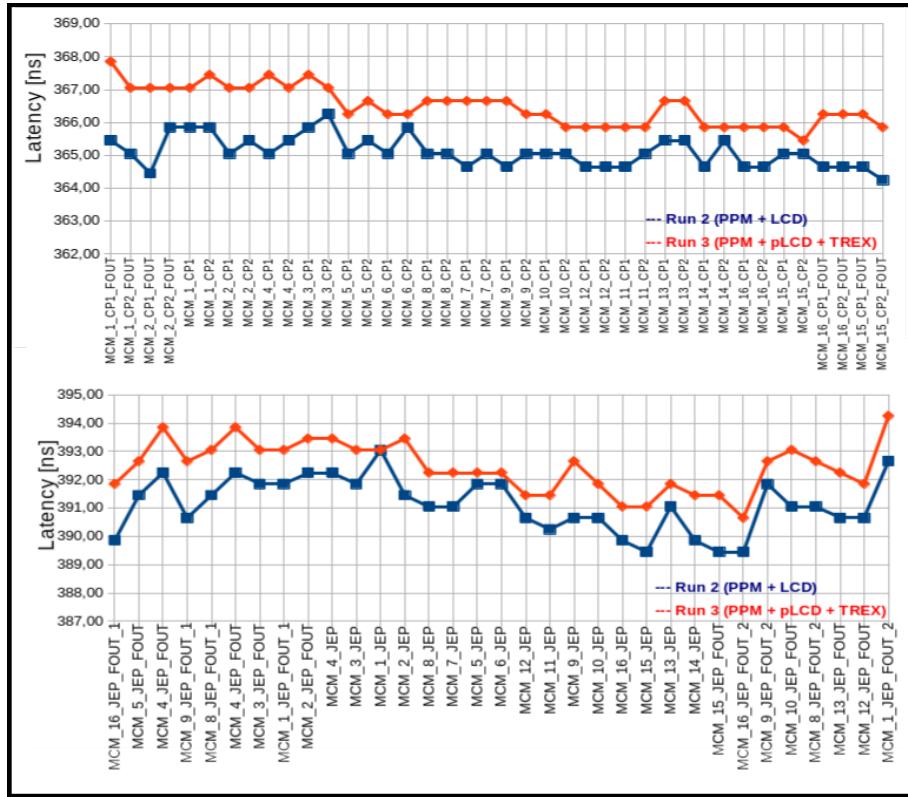

In this thesis, TREX prototypes are first monitored with regard to their operating conditions for compliance with the individual component specifications and estimation of power consumption under the greatest possible load. This results in a maximum power consumption of 43 W. Furthermore, the data reception in their main processing unit is ensured and subjected to a long-term test. The preservation of the proper bunch-crossing assignment of data and their temporal alignment is demonstrated. The optical transmission is characterised by eye diagrams and standardised IEEE requirements in stand-alone loopback and joint tests with a target processor. Bit error rates of  $1.7 \times 10^{-15}$  were measured on all transmission lines. A latency comparison to the legacy data path shows no critical increase. Safe operation of the TREX module is thus guaranteed.

# Contents

|          |                                                               |           |

|----------|---------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                           | <b>3</b>  |

| <b>2</b> | <b>The ATLAS Experiment</b>                                   | <b>5</b>  |

| 2.1      | The ATLAS Detector . . . . .                                  | 5         |

| <b>3</b> | <b>Level-1 Calorimeter Trigger</b>                            | <b>13</b> |

| 3.1      | Input Signals . . . . .                                       | 13        |

| 3.2      | Implementation in Run-2 . . . . .                             | 14        |

| 3.3      | The Preprocessor . . . . .                                    | 14        |

| <b>4</b> | <b>Run-3 Upgrades</b>                                         | <b>19</b> |

| 4.1      | Detector Upgrades . . . . .                                   | 19        |

| 4.2      | LAr Calorimeter Upgrade . . . . .                             | 20        |

| 4.3      | Upgrades of the Level-1 Calorimeter Trigger . . . . .         | 20        |

| <b>5</b> | <b>TREX Functional Tests</b>                                  | <b>25</b> |

| 5.1      | Monitoring of Operating Conditions . . . . .                  | 25        |

| 5.2      | LVDS Data Reception and Alignment in PREDATOR FPGA . . . . .  | 32        |

| 5.3      | Characterisation of Optical High-Speed Transmission . . . . . | 41        |

| 5.4      | Latency Comparison . . . . .                                  | 49        |

| <b>6</b> | <b>Summary</b>                                                | <b>51</b> |

| <b>A</b> | <b>Warning and Error Alarms</b>                               | <b>55</b> |

| <b>B</b> | <b>Lists</b>                                                  | <b>57</b> |

|          | List of Figures . . . . .                                     | 57        |

|          | List of Tables . . . . .                                      | 58        |

|          | List of Acronyms . . . . .                                    | 59        |

# Chapter 1

## Introduction

Research on the properties of matter in large and small dimensions has led in the past to a deeper understanding of processes and interrelations in nature. Physical theories mostly focus on single channels of interactions or are only valid under ideal conditions. Experiments are designed to confirm or reject the theories or to restrict them to ranges of validity. One of the most successful theories is the Standard Model (SM) of particle physics which was able to predict the existence of several particles and their properties. Its complete confirmation would not have been possible without the construction of huge accelerators and appropriate particle detectors. But known phenomena exist that can't be explained within the framework of the SM, like the presence of dark matter or the baryon asymmetry problem.

In the search for new physics beyond the SM (BSM), modern experiments produce an overwhelming amount of data. Real-world limitations make it impossible to transfer all this data to mass storage. But this is usually also not demanded. Many experiments are rather interested in rare or so far unseen events. Without an effective pre-selection based on clear criteria, the desired events can't be recorded for an offline analysis. Selection criteria are e.g. energy thresholds or the types of identified particles. Trigger systems realise this pre-selection in hardware, software or in a combination of both and are precisely concerted to the experimental conditions. If they change, also the trigger must adapt to the new situation.

This is the current scenario for the ATLAS (A Toroidal LHC ApparatuS) trigger system, which has to cope with increased event rates and harsher pile-up conditions in the course of the Large Hadron Collider (LHC) upgrades that aim to reach a higher luminosity and energy. The ATLAS trigger is grouped into two levels, with the first level consisting of fast custom-built hardware that processes calorimeter and muon detector data. The second level is the software-based High Level Trigger, that makes the final selections in use of the full detector information.

The LHC upgrades affect mainly a subgroup of the ATLAS first level trigger: the Level-1 Calorimeter Trigger (L1Calo). New front-end calorimeter readout electronics are no longer compatible with the Run-2 design. Dedicated trigger hardware, the so called Feature Extractors (FEXes), will provide optical, digital interfaces to receive information from the calorimeter electronics in finer granularity. Other calorimeter types will continue to send analogue signals until the end of Run-3, which are first routed to the L1Calo Preprocessor where they have to be digitised and converted to optical data for transmission to the FEXes. This is accomplished by Tile Rear Extension (TREX) modules that will be installed in the Preprocessor system.

Three TREX prototype modules were fabricated and fully assembled at the Kirchhoff-Institute for Physics in Heidelberg. This thesis aimed to validate TREX operation concerning different transmission lines and the operating conditions on the basis of the prototypes. Board temperatures, voltages and

currents were monitored at full load comparing the development under two different heat sinks. The reception of electrical signals on the real-time path in the main processing unit of the TREX was tested with the usage of a delay element, that was able to shift the sampling point of incoming serial streams by more than a bit length. Optical transmission was verified in stand-alone and joint tests with a FEX module, including bit error rate measurements. Standardised receiver specifications were used for this purpose. A latency comparison between the former and upgraded Preprocessor system was done to exclude timing issues on the legacy data path.

Chapter 2 starts with an overview of the ATLAS experiment. Individual detector constituents are presented in detail. Chapter 3 explains the functionality of the L1Calo trigger with a focus on the Preprocessor. The fourth chapter summarises the upgrades for Run-3 including the TREX, which makes up the largest part here. Chapter 5 presents and discusses the mentioned tests on different transmission lines and the monitoring of operating conditions. This thesis ends with a summary of the results and a little outlook of possible future modifications in the sixth chapter.

## Chapter 2

# The ATLAS Experiment

The ATLAS experiment, located at the LHC in Geneva, Switzerland is a particle detector which aims to investigate key issues of modern particle physics experimentally and to observe new phenomena beyond the Standard Model of physics. It is a general purpose detector, which is able to detect multiple hadronic and leptonic final states in proton-proton collisions in the TeV scale. This chapter gives an overview of the detector structure and the tasks of the single detector parts according to [8].

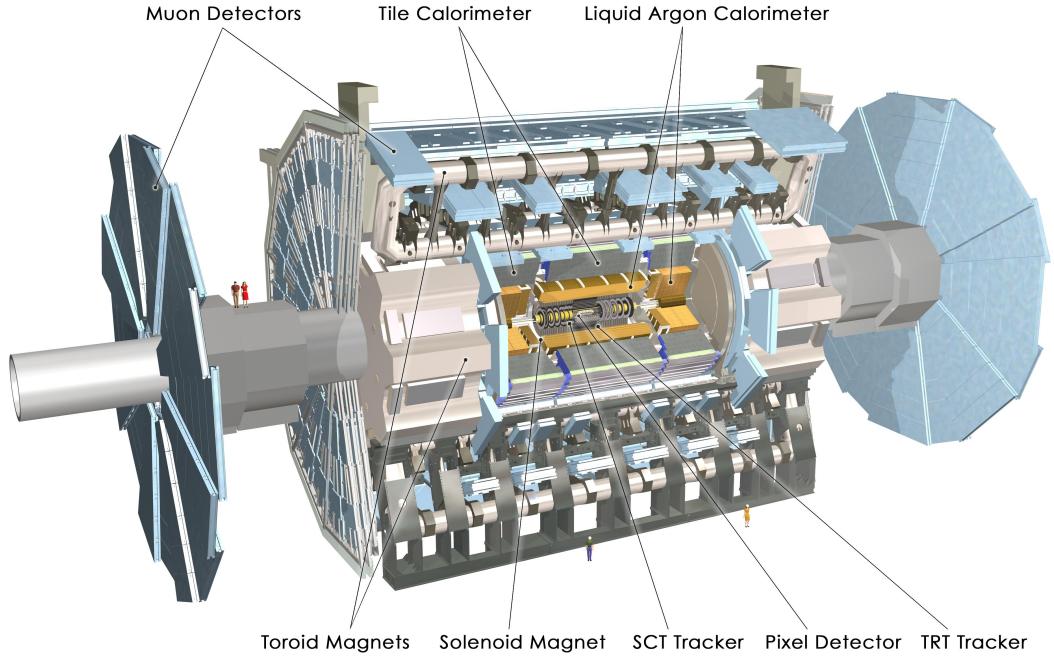

### 2.1 The ATLAS Detector

The ATLAS detector is with its dimensions of  $46\text{m} \times 25\text{m} \times 25\text{m}$  and a weight of 7000 tons the largest elementary particle detector at a collider ever built. A layout is shown in figure 2.1. The interaction point (IA) is in the middle of the detector, where the proton beams cross. It defines the point of origin for its coordinate system. The z-axis is aligned with the beam axis. The x-axis points towards the middle of the LHC ring and the y-axis points upwards. Using spherical coordinates, the polar angle  $\theta$  is usually expressed as pseudorapidity

$$\eta = -\ln[\tan(\theta/2)]. \quad (2.1)$$

This has the advantage that in the relativistic limit ( $m \ll p$ ) the pseudorapidity matches the beamline rapidity

$$y = \frac{1}{2} \ln \left( \frac{E + p_L}{E - p_L} \right), \quad (2.2)$$

where  $p_L$  is the longitudinal momentum along the beam axis. Since rapidities are additive and their differences lorentz-invariant, they are a common quantity in particle physics, whereas the pseudorapidity is easier to determine experimentally.

As the LHC delivers bunches of proton beams at a frequency of 40.08 MHz (referred to as 40 MHz from now on) with an average number of 30 to 50 particle collisions, which is even desired to be increased up to 200 within the upcoming upgrades in the near future, the technical requirements are rather ambitious. Also the different behaviour of various particle species in decay or deposition of energy makes it necessary to divide the detector into the following major parts (from inside to outside): the inner tracking detector, the electromagnetic and hadronic calorimeters, the muon spectrometer with toroid magnets and the trigger and data acquisition system, which is not shown in figure 2.1. In the following these subsystems are described in more detail.

**Figure 2.1:** Schematic layout of the ATLAS detector. Various components are labelled. Particle beams enter from the sides and interact in the middle of the detector. [1]

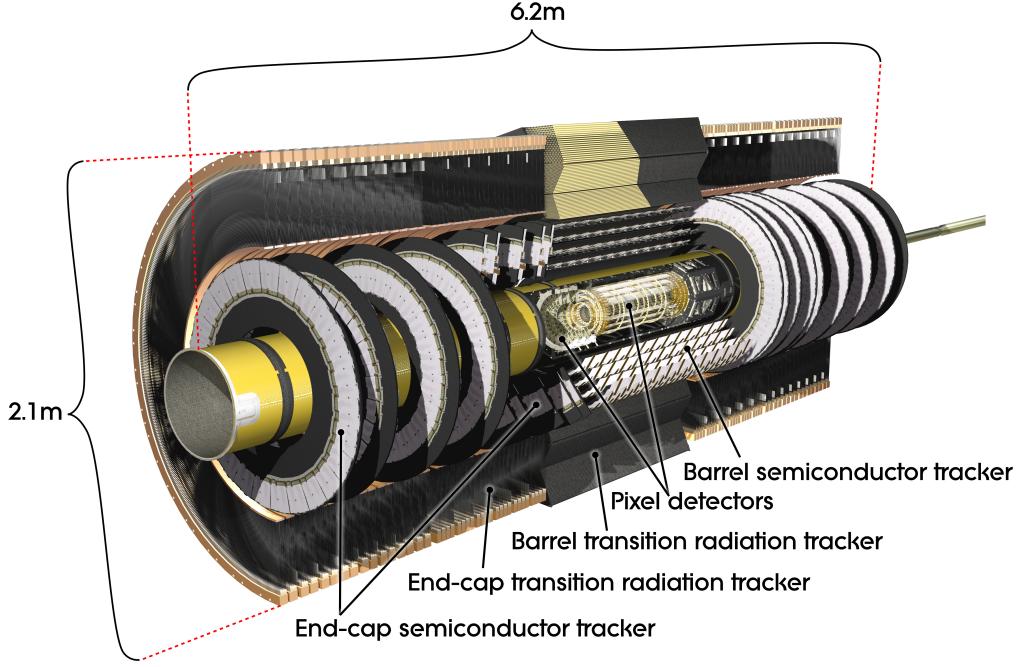

### 2.1.1 The Inner Tracking Detector

The inner detector (ID), closest to the interaction point, has the function to reconstruct trajectories of electrically charged particles which also results in a momentum measurement. Therefore, it is placed inside a 2 T magnetic field created by a solenoid magnet. In addition, the point of origin of produced particles in collisions has to be identified. To achieve an appropriate spatial resolution, the inner detector is made up of the following three stand-alone sub-detectors: the Pixel Detector, the Semiconductor Tracker (SCT) and the Transition Radiation Tracker (TRT). They complement one another to achieve high precision in all coordinates for a pseudorapidity range of  $|\eta| < 2.5$  and a transversal momentum of  $p_T > 0.5$  GeV. The relation between bending radius  $R$ , magnetic field strength  $B$  and transversal momentum  $p_T$  with unit charge is

$$p_T[\text{GeV}] = 0.3B[\text{T}]R[\text{m}], \quad (2.3)$$

concluding that particles with lower  $p_T$  are stuck inside the detector. The inner detector and its parts are illustrated in figure 2.2. The sub-detectors, which are installed in two implementations (barrel and end-cap regions), are briefly described in the following.

#### The Pixel Detector

The Pixel Detector, the innermost part, has the highest spatial resolution because of its small distance to the IA, involving a high track density. The detection method is based upon a p-n junction in reverse bias, resulting in a large depletion zone. Traversing photons or charged particles excite electrons to the conduction band, creating electron-hole pairs, which are separated through the applied voltage and detected afterwards. The total 1744 modules ( $15.5 \text{ cm}^2 \times 250 \mu\text{m}$ ) are arranged in three concentrically (barrel) or disk (end-cap) layers, where the inner barrel layer is placed 5 cm around the beam axis. The smallest size of a single pixel is  $50 \mu\text{m}$  in  $\Phi$  and  $400 \mu\text{m}$  in  $z$  or  $R$  direction, which leads to a spatial resolution of  $10 \mu\text{m}$  in the  $(R - \Phi)$  plane and  $115 \mu\text{m}$  in  $z$  direction (or  $R$  for end-cap

**Figure 2.2:** Schematic layout of the ATLAS inner detector. Pixel Detector, SCT and TRT are labelled. The detectors are either arranged concentrically around the beam axis or as end-caps at the detector’s front and back to avoid particle loss. [1]

detectors). A fourth pixel layer was installed later during LS1 (long shutdown 1) [16].

### The Semiconductor Tracker

The SCT consists of four layers in the barrel region and 18 disks in the end-caps of double-sided semiconductor microstrip sensors, where the two sides are rotated by a stereo angle of 40 mrad to get two-dimensional space point information. Two sensors form in total 768 silicon strips with a length of 12 cm, a thickness of 285  $\mu\text{m}$  and a constant pitch of 80  $\mu\text{m}$  [2]. These sensors are grouped to four to form a module and the whole SCT is made up of 4088 modules. This topology results in a resolution of 17  $\mu\text{m}$  in the  $(R - \Phi)$  plane and 580  $\mu\text{m}$  in z (barrel) or  $R$  (end-cap) direction.

### The Transition Radiation Tracker

The TRT is a combination of a transition radiation detector and a drift chamber. The basic detector elements are straw tubes with a 4 mm diameter and a 31  $\mu\text{m}$  thick gold plated tungsten anode wire in the centre. The straw tube wall forms the cathode with a 0.2  $\mu\text{m}$  Al layer. They are filled with a gas mixture of 70 % Xe, 27 % CO<sub>2</sub> and 3 % O<sub>2</sub> with a bit over pressure. The volume between the tubes is stuffed with 19  $\mu\text{m}$  fibres (barrel) or 15  $\mu\text{m}$  foils (end-cap) made out of polypropylene, functioning as a radiator to increase signals of the transition radiation effect. In the barrel region the straw tubes are grouped up to 73 layers with a length of 144 cm parallel to the beam axis, whereas there are 160 radially layers in the end-caps with a length of 37 cm. This design leads to a measurement only in the  $(R - \Phi)$  plane with an accuracy of 130  $\mu\text{m}$ , leaving 36 hits per track for charged particles with transverse momentum  $p_T > 0.5$  GeV and pseudorapidity  $\eta < |2.0|$ . Since the transition radiation depends on the Lorentz factor  $\gamma = E/m$ , the strongest contribution comes from electrons with photon energies up to 30 keV. These photons can be absorbed by the Xe in the straw tubes, giving a characteristical signal for electron identification besides the TRT function as a tracker.

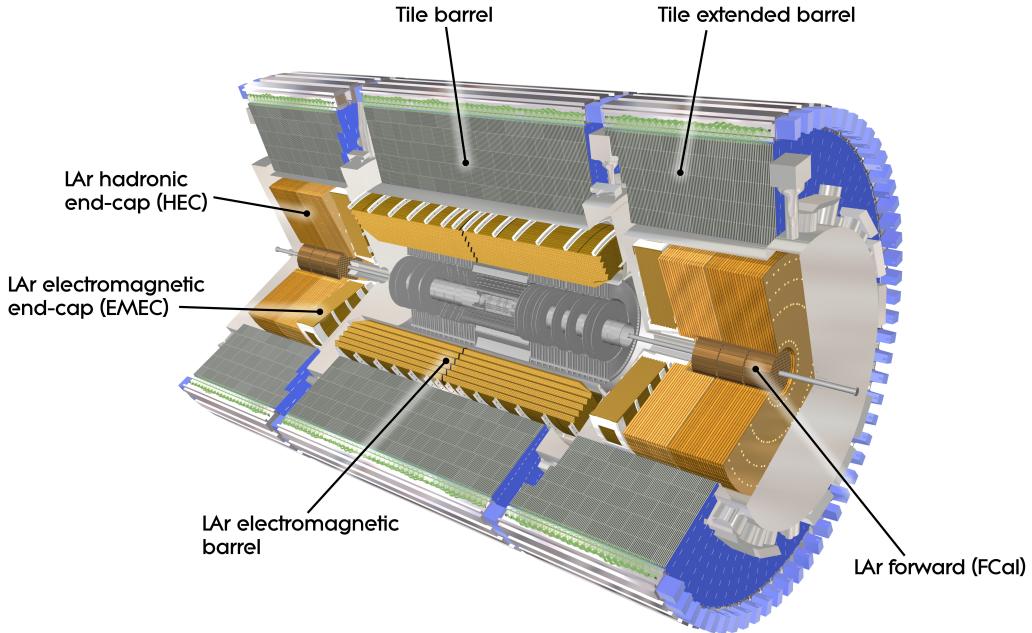

**Figure 2.3:** Schematic layout of the ATLAS calorimeters. The LAr detectors are shown in orange, where electromagnetic and hadronic parts are indicated by slightly different colours in the end-cap regions. The hadronic Tile calorimeter is shown in blue from the side. The ID is greyed out. [1]

### 2.1.2 Calorimetry

The calorimeters perform the destructive energy measurement of particles created in the proton-proton collisions. ATLAS uses sampling calorimeters, which are constructed from alternating layers of dense absorber and active sampling material. They cover the pseudorapidity range  $\eta < |4.9|$  by their size of 12 m in length and 4.25 m in the outer radius. As shown in figure 2.3, the calorimetry is subdivided into two main parts: the electromagnetic (ECAL) and the hadronic calorimeter (HCAL). Again, both calorimeter types are installed as barrel or end-cap implementations. The functionality of both is explained in the sections below.

#### The Electromagnetic Calorimeter

The ECAL measures precisely the energy deposition of electrons and photons. All of its modules use liquid argon (LAr) as active sampling and lead as absorber material. The different layers are arranged in an accordion shape resulting in a nearly equal response signal independent of the particle's direction of travel. At energies beginning from 1.022 MeV, electrons lose their energy mainly through bremsstrahlung and pair production in the absorber, generating a cascade of secondary particles. At lower energies ionisation and the photoelectric effect dominate. To collect the ionisation charges, a voltage of 2 kV is applied between two copper electrodes in the LAr layer. A third electrode in the centre does the readout via capacitive coupling.

The electromagnetic barrel (EMB) and end-cap calorimeter (EMEC) together cover a pseudorapidity range of  $|\eta| < 3.2$ . They have a total thickness of 22 to 33 radiation lengths  $X_0$ , varying for different  $\eta$  regions. Because of the big amount of produced particles in collisions and the demand for an appropriate resolution, the  $\Delta\eta$  granularity of the EMB increases towards the beam line. It reaches from 0.003 at the inner surface to 0.05 at the outer one. In the EMEC the  $\Delta\eta$  granularity varies from 0.003 to 0.1. In  $\Delta\Phi$  the granularity reaches from 0.025 to 0.1. In order to take energy losses in the

ID into account a presampler is placed in front of the ECAL, which is in the end just one LAr layer of 11 mm thickness. With all this implementations the ECAL reaches an energy resolution of

$$\frac{\sigma(E)}{E} = \frac{10\%}{\sqrt{E}} \oplus 0.17\%. \quad (2.4)$$

The constant term arises due to non-uniformities in the ECAL response.

### The Hadronic Calorimeter

The ATLAS HCAL consist of three parts: the Tile calorimeter, the LAr end-cap calorimeter (HEC) and the LAr forward calorimeter (FCal).

The Tile calorimeter is constructed around the ECAL and has alternating layers of steel absorbers and plastic scintillators. Deposited energy excites molecules in the scintillator, which send out photons at deexcitation. Since they are usually in the UV scale, wave length shifters are added to convert the UV photons to visible light. Additionally, the photons are collected by fibres which also apply a wave length shift and route them to photomultipliers (PMTs). Since the physical processes for hadronic showers differ from electromagnetic showers, even electrically charged hadrons won't lose all their energy in the ECAL, mainly because of their high mass. This demands for a detector that is big enough to contain the whole hadronic shower. Therefore, the Tile calorimeter has a radial thickness of about 7.4 hadronic interaction lengths  $\lambda_{\text{had}}$ . But still with these dimensions neutrinos and muons will escape the Tile calorimeter. In the case of the neutrinos (and potentially dark matter) this leads to missing energy in the evaluation of the measurements.

The HEC has copper absorbers and is installed in the range  $1.5 < |\eta| < 3.2$  with a thickness of  $12 \lambda_{\text{had}}$ . The FCal covers the highest  $\eta$  ranges up to  $|4.9|$  and uses copper absorbers in the first layer because it is optimised for electromagnetic showers, but also tungsten for the following layers. It reaches a thickness of  $10 \lambda_{\text{had}}$ .

The whole HCAL  $\Delta\eta \times \Delta\Phi$  granularity varies from  $0.1 \times 0.1$  to  $0.2 \times 0.2$  for different subcalorimeters and  $\eta$  ranges. The energy resolutions are now different for different particles. As a reference the resolution for charged pions are provided.

$$\begin{aligned} \text{Tile calorimeter: } \frac{\sigma(E)}{E} &= \frac{52.7\%}{\sqrt{E}} \oplus 5.7\%. \\ \text{HEC: } \frac{\sigma(E)}{E} &= \frac{70.6\%}{\sqrt{E}} \oplus 5.8\%. \\ \text{FCal: } \frac{\sigma(E)}{E} &= \frac{70.0\%}{\sqrt{E}} \oplus 3.0\%. \end{aligned} \quad (2.5)$$

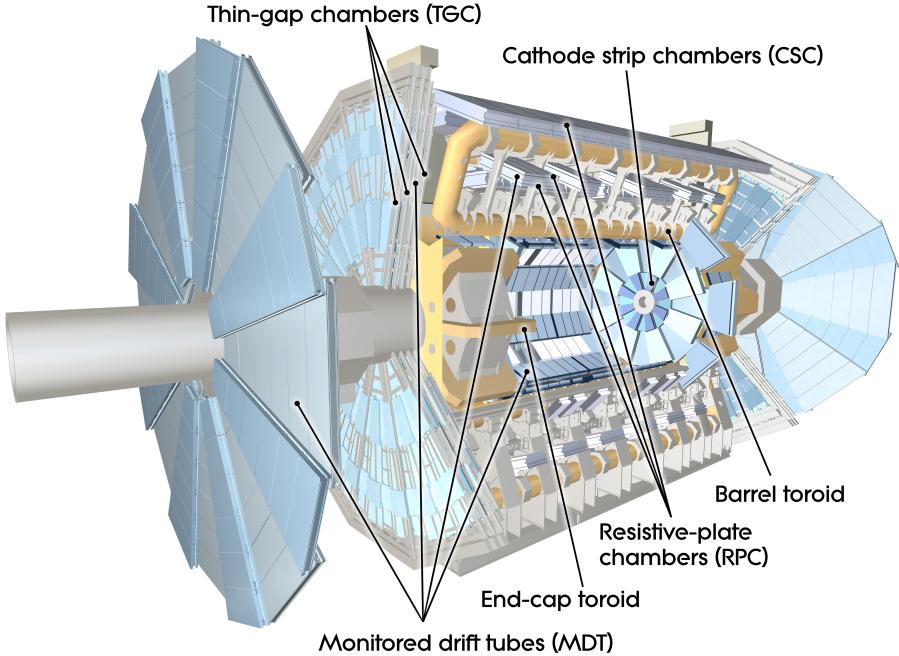

### 2.1.3 The Muon Spectrometer

Since muons interact electromagnetically one could naively expect that they are covered by the ECAL when created at the IA. But due to their high mass they lose only little energy via bremsstrahlung, leaving the ID and calorimetry nearly unaffected. The same holds for secondary muons produced in particle showers. Therefore it requires an additional system to take muons or other charged particles into account that eventually pass the calorimetry. In order to measure their momentum, a magnetic field in the range  $|\eta| < 2.7$  is created by superconductive toroid magnets with eight coils each for barrel (0.5T) and end-cap regions (1T). Apart from tracking, the muon system does bunch-crossing identification and triggering for defined  $p_T$  thresholds at  $|\eta| < 2.4$ . So the entities of the muon system can be divided into precision-tracking chambers and trigger chambers.

**Figure 2.4:** Conceptual layout of the ATLAS Muon Spectrometer. Toroid magnets are illustrated as yellow loops. Tracking and trigger chambers are greyish blue [1].

### Precision-tracking chambers

Tracking is mainly achieved via Monitored Drift Tubes (MDTs) which are cylindrical tubes filled with a gas mixture of Ar and CO<sub>2</sub> that is ionised by traversing muons. Charges are collected by a central anode wire with an applied voltage of approximately 3 kV between anode wire and cathode tube walls. While the spatial resolution of a single tube is 80  $\mu\text{m}$ , MDTs are grouped to chambers with up to eight consecutive segments of tubes achieving a spatial resolution of 35  $\mu\text{m}$  per chamber. In the barrel region the MDT chambers are installed in three concentric layers between and on the coils of the toroid magnets, while for the end-cap regions they are installed as four disks before and behind the magnets. Only for the innermost end-cap disk Cathode Strip Chambers (CSCs) are used instead of MDTs in the region  $2.0 < |\eta| < 2.7$  (compare figure 2.4). CSCs are also gaseous detectors constructed as multiwire proportional chambers with segmented cathode strips orthogonal to the anode wires. They allow a higher rate capability and granularity compared to the MDTs, which is needed for high  $|\eta|$  and small distances to the IA. Their spatial resolution is 40  $\mu\text{m}$ . The precision tracking with applied magnetic field allows a momentum resolution of about 10% for 1 TeV tracks.

### Trigger chambers

For triggering, the muon system is complemented by Resistive Plate Chambers (RPCs) in the barrel and Thin Gap Chambers (TGCs) in the end-cap region. They are designed for short readout times in the range of tens of nanoseconds with small spreaded signals to identify the bunch-crossing. The design principle of RPCs is a gaseous detector with two parallel plates in a distance of 2 mm and an applied voltage of 9.8 kV. They are mounted together with the MDT chambers in the second, where they surround them, and the third concentric layer. In contrast TGCs are multiwire proportional chambers with a smaller distance between wire and cathode plates then the wire-to-wire distance, resulting in small drift times. One TGC is placed in front of the first tracking disk, while another is placed in front and two are placed after the second disk.

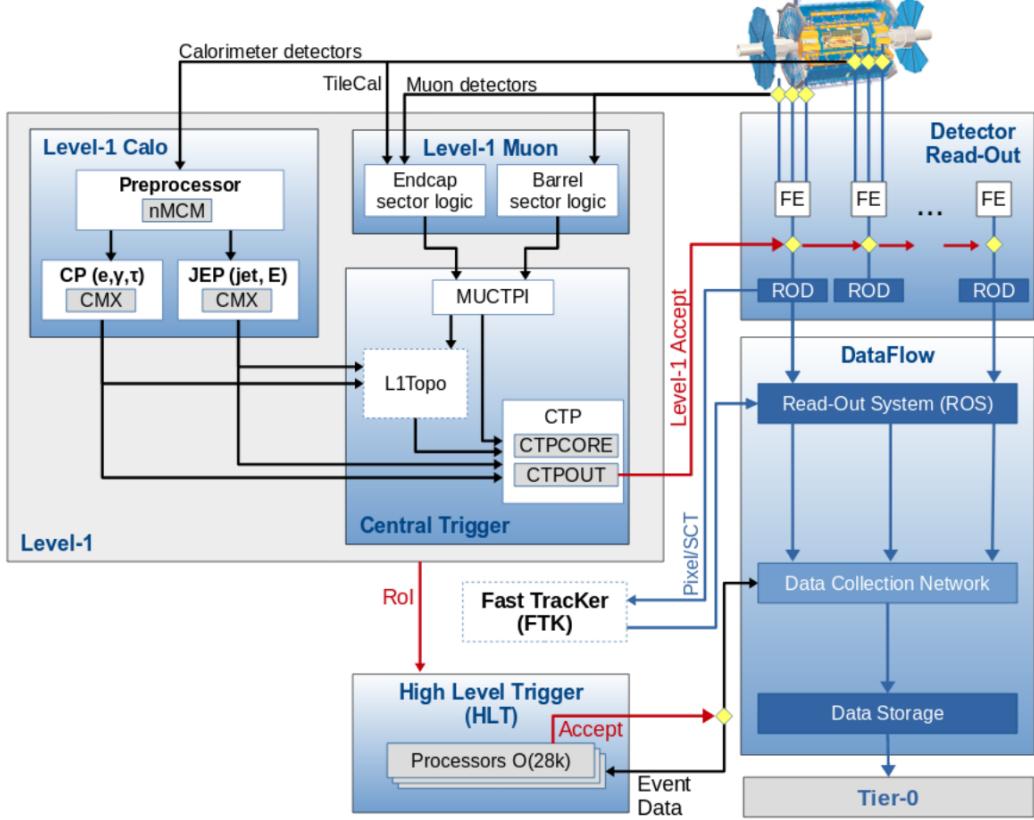

**Figure 2.5:** Overview of the ATLAS TDAQ system in Run-2. FTK was in Run-2 still under commissioning [3].

### 2.1.4 Trigger and Data Acquisition System

Trigger and Data Acquisition (TDAQ) is a substantial task in collider experiments as it reduces the initial amount of raw data by separating interesting event candidates from background. With about  $10^8$  readout channels the overall output of the ATLAS detector is also way too big to write everything to data storage. In Run 2 the whole trigger system, illustrated in figure 2.5, reduces the bunch-crossing frequency of 40.08 MHz to approximately 1 kHz in two stages. The first stage is the Level-1 (L1) trigger. It is realised by custom hardware and receives signals on trigger tower basis from the calorimeters and the muon detector. Upon a selected event an L1 Accept signal (L1A) is send within  $2.5 \mu\text{s}$  to the subdetectors which starts the readout to pipeline memories. Based on the decisions of the second stage, the High Level Trigger (HLT), the buffered data is rejected or transferred to data storage for offline analysis. The HLT is software running on commercial computer farms using calorimeter information in finer granularity but also tracking data from the ID for its decisions.

The L1 Trigger can be further subdivided into L1Calo, L1Muon and Central Trigger. Of main interest for this work will be the L1Calo trigger, especially its Preprocessor and upgrades, that will be the content of the next chapters.

# Chapter 3

## Level-1 Calorimeter Trigger

As a part of the first level the L1Calo trigger is involved in the primary event selection looking for signatures of electrons, photons,  $\tau$  leptons and jets with high transversal momentum in the calorimeters. It also computes the total transverse energy  $\Sigma E_T$  and the missing transverse energy  $E_T^{miss}$ , which occurs due to neutrino production or possible dark matter objects. In the following sections an overview of the L1Calo architecture and its input signals is given as described in [8] and [10]. Section 3.3 on the Preprocessor also used [12] and [26] as a reference.

### 3.1 Input Signals

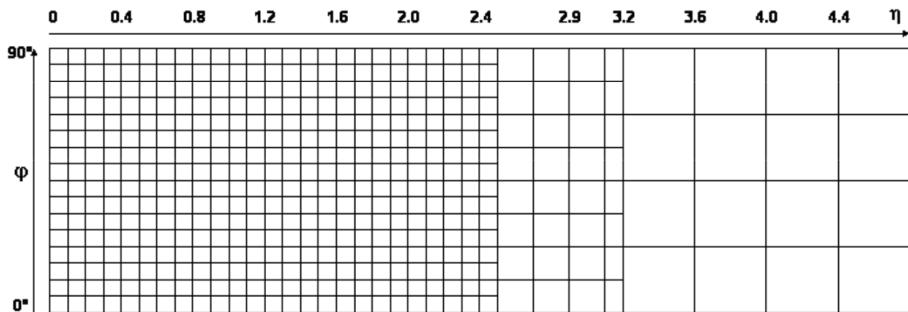

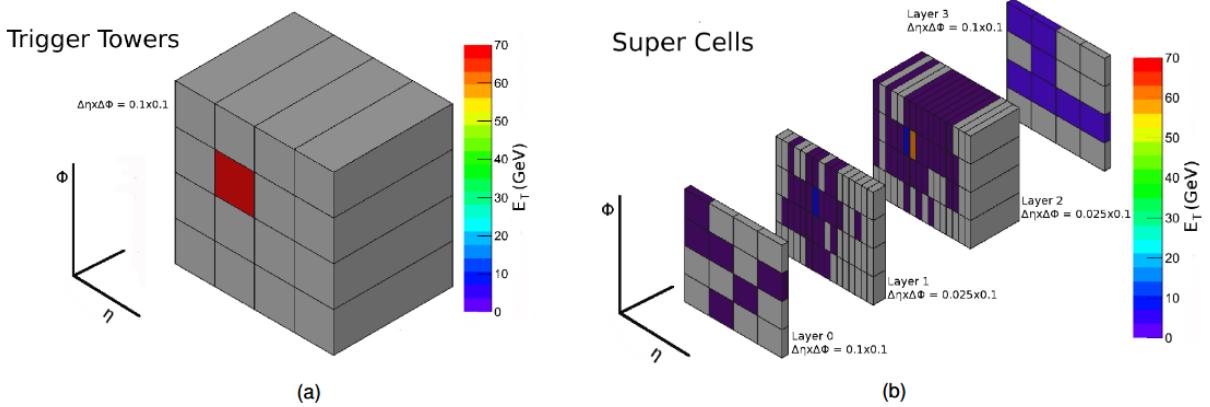

The L1Calo trigger receives analogue input signals from both calorimeters. The signals are not send by the single calorimeter cells but first summed up to trigger towers in the front-end electronics. At  $|\eta| < 2.5$  the granularity of these signals is  $0.1 \times 0.1$  in  $\Delta\eta \times \Delta\Phi$  but gets coarser at larger pseudorapidity, shown in figure 3.1. Such a tower covers the full depth of the corresponding electromagnetic or hadronic detector parts. By this procedure 7168 trigger tower signals are formed in total, each describing  $E_T$  values in multiple calorimeter cells for ECAL and raw energy for HCAL. The resulting trigger tower

**Figure 3.1:** Trigger tower granularity for  $\eta > 0$  and one quadrant in  $\Phi$ . [10].

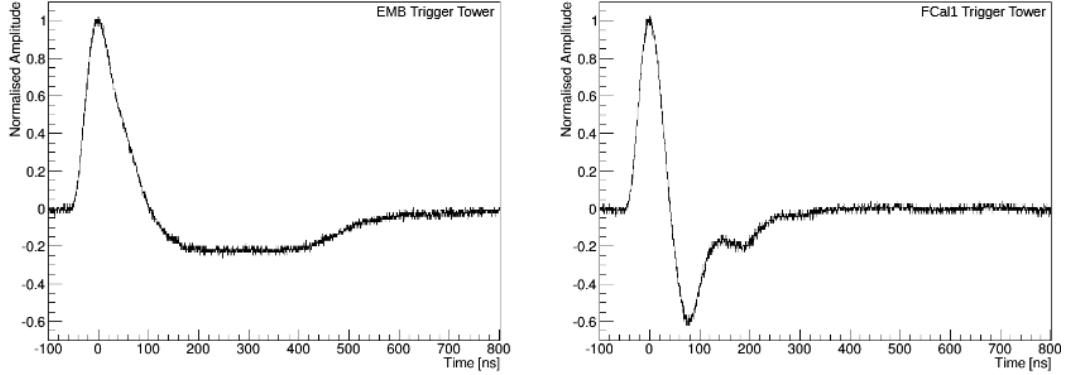

pulses are in general of bipolar shape. The integrals of the positive and negative part match due to charge conservation. Figure 3.2 exemplifies the pulses for EMB and FCAL. The shape inequalities of individual detector parts result from different detector geometries. Pulses of the Tile calorimeter look like the positive part of the EMB with a longer but therefore lower undershoot, so that it can be usually ignored.

**Figure 3.2:** Bipolar trigger tower pulses for EMB (left) and FCAL (right) [26].

## 3.2 Implementation in Run-2

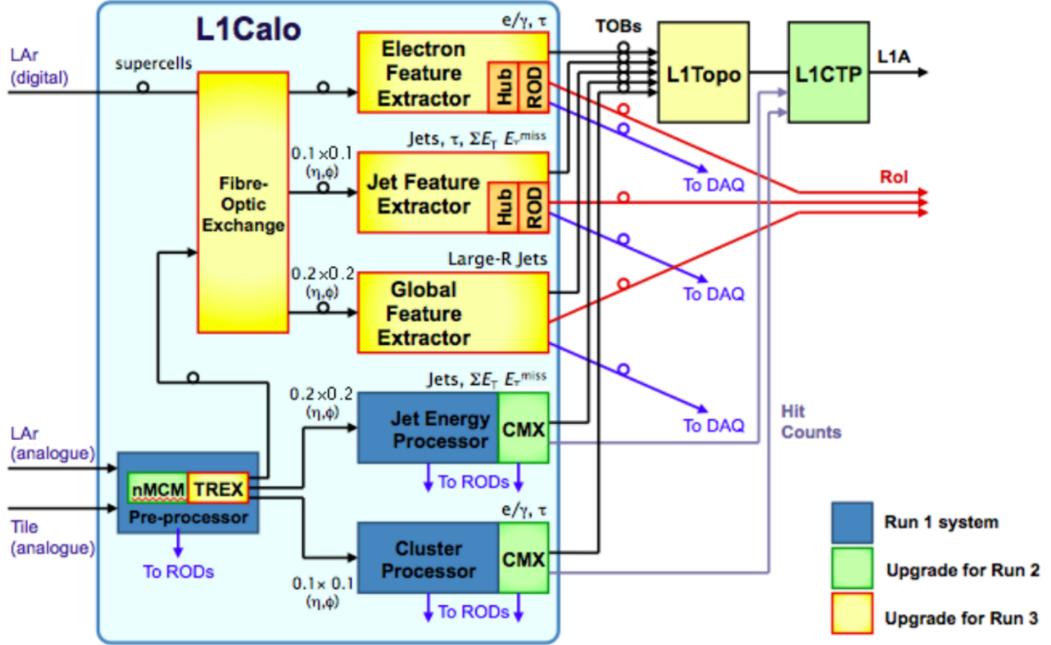

As it can be seen in figure 2.5, the L1Calo trigger consists in Run-2 of three subsystems:

1. The Preprocessor which mainly digitises the incoming analogue calorimeter signals, assigns a transversal energy value  $E_T$  and determines the bunch-crossing (BC).

2. The Cluster Processor (CP) which identifies electrons, photons,  $\tau$  leptons and hadrons.

3. The Jet/Energy Processor (JEP) which provides identification of jets and computes the total, the missing and the sum  $E_T$  values.

Whereas the Preprocessor tasks are self-contained, the CP and JEP have some commonalities. They are both performing sliding window algorithms. For CP such a window is composed by  $4 \times 4$  trigger towers while JEP uses so called jet elements which are a summation over  $2 \times 2$  trigger towers, so that one jet element covers a granularity of  $0.2 \times 0.2$  in  $\Delta\eta \times \Delta\Phi$ . JEP window sizes vary from  $2 \times 2$  to  $4 \times 4$  jet elements. Basically these algorithms look, in steps of one in  $\eta$  or  $\Phi$  direction, for the exceedance of definable energy thresholds of neighbouring trigger tower or jet element sums across their assigned area. Additional isolation criteria can be applied. By this method, CP and JEP produce results in form of Trigger Objects (TOBs) which contain information about energy, location and the type of particle. TOBs are forwarded to the Central Trigger which adds similar information from L1Muon and makes the final L1 trigger decision.

For a proper performance the whole azimuthal coordinate range is divided into four quadrants. To avoid efficiency loss across quadrant boundaries, some trigger towers and jet elements are duplicated by the Preprocessor. In the end, the CP is realised in four crates each containing 14 modules and the JEP in two crates with 16 modules each. One CP crate and eight JEP modules cover one  $\Phi$  quadrant respectively.

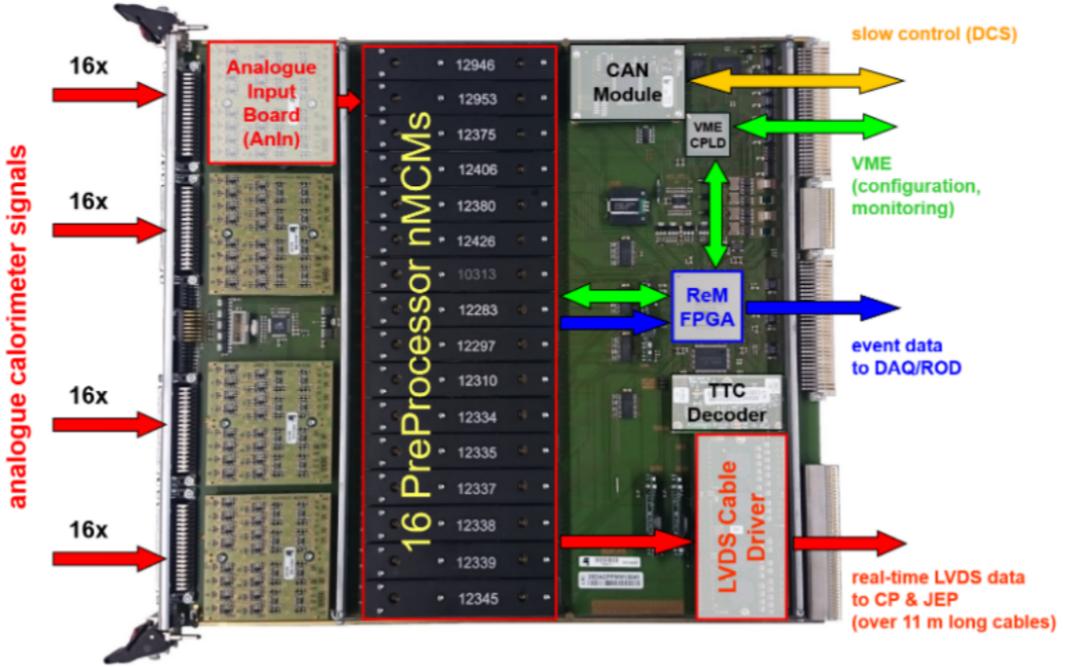

## 3.3 The Preprocessor

The complete Preprocessor system is distributed over 124 hardware-identical Preprocessor Modules (PPMs) in eight VME<sup>1</sup> crates, where six crates are assigned for LAr and the others for the Tile calorimeter. Each crate has in addition a Timing Control Module (TCM) that distributes information such as the BC-clock (40 MHz), L1A or counter reset signals over the VME backplane. A single board computer acts as crate controller for configuring and controlling of the PPMs via the VME interface.

---

<sup>1</sup>Versa Module Eurocard.

**Figure 3.3:** The Preprocessor Module. Real-time path elements are marked in red, the readout path in blue, communication to DCS in yellow and the VME path for board configuration or lab monitoring in green.

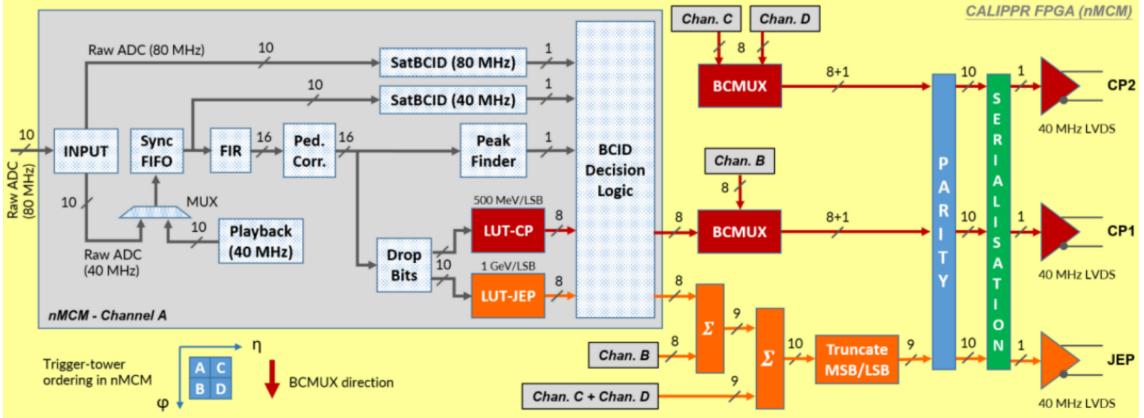

All signal processing paths on the PPM are illustrated in figure 3.3. The analogue trigger tower pulses are received as differential signals, having the advantage of low electromagnetic susceptibility since interfering signals should have the same impact on both wires. These signals come with amplitudes up to 2.5 V corresponding to a maximum  $E_T$  value of 255 GeV. In a first step, up to 64 differential signals are converted to single ended form by operational amplifiers on four Analogue Input (AnIn) boards. A fixed gain is applied to fit the 1 V digitisation range and a digital-to-analogue converter (DAC) may add a voltage offset to have an uniform baseline for all channels. Next, the signals are routed to the new Multichip Modules (nMCMs), the main processing units on the PPM. They were installed during LS1, replacing the prior modules based on application-specific integrated circuits (ASICs) by newer ones based on field programmable gate arrays (FPGAs). A PPM contains 16 nMCMs each handling four trigger tower signals. After digitisation with 10-bit resolution at the doubled BC frequency (80 MHz), the results are received by the Calorimeter Information Preprocessor (CALIPPR) FPGA. Figure 3.4 demonstrates its processing paths. An overview of the most important tasks follows.

- Synchronisation of trigger tower pulses: The signals arrive asynchronously due to different time-of-flights from the IA to the particular calorimeter cells and different cable lengths from calorimeters to the PPM. For a proper BC-wise L1 decision, these signals have to be aligned in time. A coarse alignment is achieved by a First In - First Out (FIFO) pipeline using the BC-clock to end up with delays in 25 ns steps. Fine time adjustment is achieved by delaying the sampling points of the analogue-to-digital converters (ADCs) in steps of 1.042 ns with a generated clock-like signal.

- Bunch-crossing identification (BCID): As shown in figure 3.2, the trigger tower pulses are multiple bunch-crossings wide. For a correct  $E_T$  extraction the peak maximum has to be identified and connected to the right BC for a proper trigger functionality. Several logical blocks are assigned to this task. For unsaturated pulses a finite impulse response (FIR) filter in combination

**Figure 3.4:** Functional behaviour of the CALIPPR FPGA real-time path. Various trigger tower signals are indicated by channel labeling. Transmission paths to CP are marked in red while orange paths show transmission to JEP. The Playback is a configurable memory used for test purposes [12].

with a peak finder algorithm is used. The FIR filter weights five consecutive ADC samples with pulse optimised coefficients and adds them up. The peak finder then simply searches for the first maximal value of three successive FIR outputs. Other values are set to 0. Saturated pulses are treated separately by looking at the rise times of the unfiltered ADC signals. Before reaching saturation, these signals are compared against defined thresholds to estimate the rise time of the pulse and the peak maximum, which is necessary if a signal saturates for several BCs. An additional option, although never been in use, is a voltage comparator on the AnIn boards with just one logical output. CALIPPR then detects the crossing over a defined threshold.

- Noise and pedestal correction: Contribution from thermal noise and pile-up effects have to be considered for a proper trigger functionality, since they adulterate the trigger tower signals. At ATLAS, thermal noise is of the order of 200 to 400 MeV. But the signal-to-noise ratio is optimised by the FIR filter coefficients. Pile-up effects vary with distance to the IA and trigger tower sizes and are considered by a dedicated algorithm, which works BC-wise for each channel. This algorithm computes an average filter output and subtracts a configurable constant from it that stands for the expected pedestal value. The filter outputs are then subtracted by this difference, giving the corrected values.

- Identification of deposited  $E_T$ : FIR filter outputs are 16-bit values that are reduced to ten bits in the first instance. This reduced value is then mapped to an transversal energy using a look-up-table (LUT), one for CP and one for JEP side respectively. Such a LUT is a  $1024 \times 8$  memory, so that each reduced FIR input is mapped to an 8-bit energy value up to 255 GeV. These LUTs show in principal a linear behaviour, but a noise cut is applied assigning an output of zero to low energy peaks. Separate LUTs for CP an JEP allow an independent configuration and calibration which effects the trigger selectivity.

- Bunch-crossing multiplexing (BCMux): The  $E_T$  results for two channels on CP side are multiplexed into one serial stream. An additional bit, the BCMux flag, is sent to indicate which channel is sending the current data.

- Jet Sums: Since JEP uses jet elements instead of trigger towers, the  $E_T$  results have to be preprocessed before sending them to JEP. For unsaturated values the sum of four trigger tower channels is computed, giving a 10-bit value. If one of the trigger towers is saturated the summed

value is set to maximum, preserving saturation. Before transmission to JEP, the most or least significant bit is dropped to end up with nine bits like for the CP with energy and BCmux flag.

- Low Voltage Differential Signaling (LVDS) transmission: To ensure an error free transmission one odd parity bit is packed together with the actual data. It is set to 1 if the number of 1s in the data is odd, otherwise it is set to 0. A defective transmission can thus be detected on receiver side if the number of changed bits is odd. When it comes to serialisation, the actual data is enclosed by a start (logical 1) and stop bit (logical 0), so that the receiver knows how to pick data. In a last step these twelve bits are converted to differential form and transmitted with 480 Mbps at low voltage.

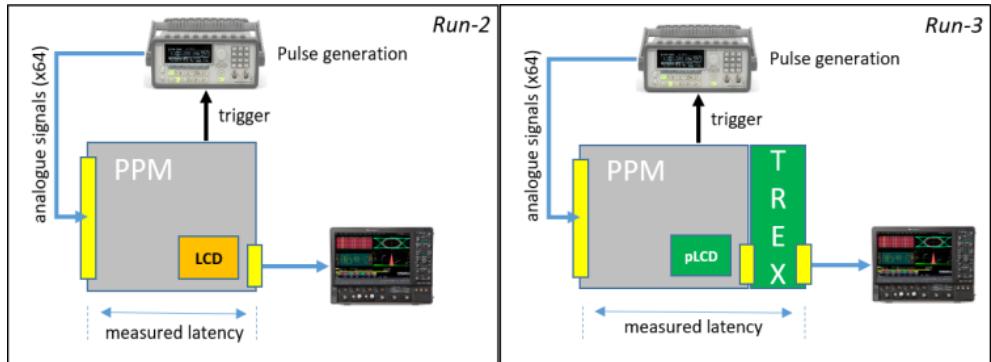

What is missing up to this point is the duplication of trigger towers or jet elements across  $\Phi$  quadrants. This tasks is adopted by the LVDS cable driver (LCD) board, more precisely by four Xilinx FPGAs on the LCD. It receives in total 48 LVDS streams from the nMCMs, fans out the required signals and drives them over 11 meter long cables. Furthermore, the LCD compensates transmission losses by amplifying the signals.

In order to validate and calibrate the PPM trigger decisions, the sampled data and assigned energy have to be checked. This is why dedicated pipeline memories are integrated on the nMCM that are buffering the data for 128 BCs. Upon an L1A, which is on-board distributed by the Trigger, Timing and Control (TTC) decoder, the Readout Manager (ReM) FPGA collects the data from both pipelines, formats it and transmits it to the DAQ via a Readout Driver (ROD) module that does not belong to the Preprocessor itself.

The ReM FPGA and also a Complex Programmable Logic Device (CPLD) are furthermore involved in configuration and lab monitoring via VME. They handle the addressing and data transfer of the programmable locations. The single board computer acts as the VME controller.

Finally the PPMs themselves have to be monitored to guarantee smooth functioning. This is done during operation by the ATLAS Detector Control System (DCS), which is even able to power down the boards. A Fujitsu micro-controller, located on the PPM between the two middle AnIn boards, gathers all accessible information like temperatures and voltages and sends it to DCS via an CAN<sup>2</sup>-bus interface.

At the end of this chapter the playback memory in the CALIPPR should be emphasised. It is a 256 register memory and can be used as an alternative input. Data is loaded from VME to configure it channel- and BC-wise for an unambiguous identification of links and is injected in the real-time path upon request. The playback is used for several test applications that will appear in this thesis.

---

<sup>2</sup>Controller Area Network

# Chapter 4

## Run-3 Upgrades

The discovery of the Higgs boson at the LHC by the ATLAS and CMS experiment in 2012 opened a new unexplored area to particle physics. In order to increase the potential for discoveries and to improve precision on measurement, the LHC will undergo substantial upgrades in the next years to reach a higher luminosity and energy. For Run-3, starting from 2021, the luminosity will be approximately increased by a factor of two to  $3 \cdot 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$ , resulting in higher event rates and harsher pile-up conditions. The ATLAS trigger system has to cope with this new experimental environment to maintain a high efficiency. The Run-3 upgrades focus mainly on improvements of the trigger and readout electronics, satisfying also requirements beyond Run-3. Nevertheless, some parts of the detector will be enhanced too. This chapter gives an overview of the upgrades during the second long shutdown (LS2) period as described in [4] and [7]. Section 4.3 is mainly based on [11].

### 4.1 Detector Upgrades

The increased event rates and pile-up after LHC upgrades will be especially challenging for the innermost detector parts. At high  $\eta$ , where background rates are high due to slightly scattered or unscattered beam particles, the detector performances is severely affected. For the muon system this affects the so called small wheel region. In figure 2.4, this corresponds to the first end-cap disk where the CSCs are mounted. In order to keep up with the expected particle rates of  $15 \text{ kHz/cm}^2$  at High-Luminosity LHC (HL-LHC) and to reduce fake trigger events a New Small Wheel (NSW) will be installed. It uses micro mesh gaseous structures (Micromegas) as tracking and small-strip TGCs as trigger elements. Micromegas use a mesh to divide the detection volume in a cell into a amplification and a conversion gap with a high ratio of their electric fields. Ions created in the conversion gap are then collected by the mesh while electrons reach the amplification gap, starting an avalanche which is detected by electrodes. Small-strip TGCs use the same detection principle as explained in section 2.1.3 but with enhanced performance. Both detector types have proven to satisfy the demanded conditions. Another innovation is planned to be improved: the ATLAS forward proton detector (AFP). It aims to identify events with intact protons at high  $\eta$ . Such processes are associated with the so far not well understood elastic and diffractive scattering. It allows the testing of Quantum chromodynamics (QCD) and BSM models. On each side of the IA two stations at respective distances of 206 and 214 m will be installed, that can be retracted during proton injection and inserted when the beam is stable. The first station is a pure silicon tracker while the second combines tracking and timing detectors. This design allows to measure the momentum, angle and time-of-flight of protons from pp interactions. The AFP was already partially operating in Run-2 with missing time-of-flight systems that were not installed due to lacking vacuum tightness of PMTs. This will be integrated for Run-3.

**Figure 4.1:** Energy deposition and reported signature of a 70 GeV electron in the current trigger towers (a) and in the upgraded super cells (b) [5].

Although it was planned to commission the Fast Tracker (FTK) earlier, it is now being finalised in the Run-3 upgrades. The FTK will be part of the TDAQ system and aims to provide fast tracking information from the ID as input to the HLT for every L1A. It will be realised by custom hardware and will operate for tracks with a transversal momentum  $p_T$  bigger 1 GeV/c within 100  $\mu$ s. FTK will implement pattern recognition algorithms that match ID information to simulated tracks, stored in on-board memory chips.

## 4.2 LAr Calorimeter Upgrade

The LS2 upgrades of the LAr calorimeter will not improve the detector itself but rather aim to increase the quality of calorimeter-based L1Calo trigger decisions. To achieve this, LAr will provide information in finer granularity replacing the former trigger towers by so called super cells. A single tower is replaced by ten super cells by dividing the tower into four layers in transversal direction. The two inner layers are furthermore subdivided into cells with a granularity of  $0.025 \times 0.1$  in  $\Delta\eta \times \Delta\Phi$ . Figure 4.1 demonstrates the difference in signature for a 70 GeV electron in trigger towers and super cells. This new architecture will allow to make use of new sophisticated algorithms enhancing jet rejection and pile-up correction. The readout of calorimeter cells in the new design requires a complete rework of the front-end electronics. For a faster transmission data is sent optically via a distribution system, called Fibre Optics eXchange (FOX), directly to L1Calo at 11.2 Gbps.

The L1Calo Preprocessor was designed for electrical input and thus can not receive the new optical signals. Also processing of more granular signals demands for changes, concluding that L1Calo has also to be updated to keep up with the increased requirements.

## 4.3 Upgrades of the Level-1 Calorimeter Trigger

New electronics must be developed for the reception of fine-granular optical LAr data. L1Calo is expanded by three FEXes (Feature Extractors) during LS2 which receive data directly from the LAr calorimeter. The tasks of CP and JEP are taken over by the electron FEX (eFEX) and the jet FEX (jFEX). A global FEX (gFEX) is searching for large-area jet objects. Figure 4.2 illustrates the old and new architecture.

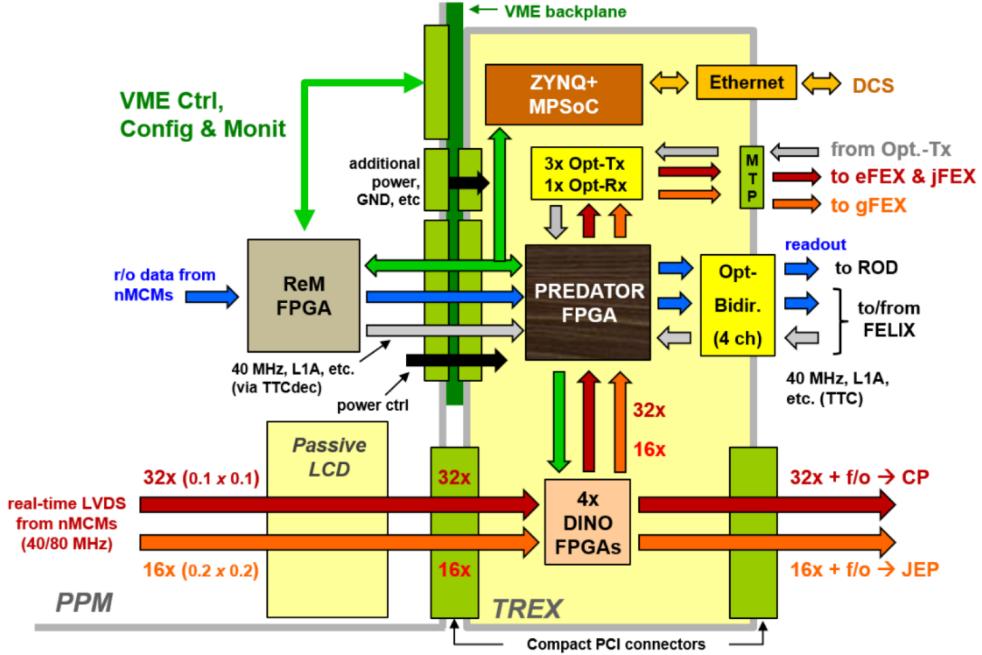

Since the FEXes need also data from the Tile calorimeter, which continues to send analogue signals on trigger tower basis until the end of Run-3, the Preprocessor will be extended to provide Tile data optically. To achieve this, TREX (Tile Rear EXtension) modules will be installed in LS2. A

**Figure 4.2:** L1Calo architecture in Run-3. Elements in yellow show the new L1Calo constituents for Run-3. Elements in blue and green were used in previous runs [6].

TREX module is an 18-layer PCB<sup>1</sup> equipped with state-of-the-art FPGAs and optical transmitters. Until commissioning and validation of the upgrades the new and the legacy system will operate simultaneously. CP, JEP and the PPMs that receive analogue LAr data will be removed accordingly. After Run-3, the current Preprocessor plus extension will be replaced by custom Tile electronics similar to LAr. In the following TREX and its components are discussed in detail.

## Tile Rear Extension

A schematic overview of TREX and its components is given in figure 4.3. As the Preprocessor upgrade only affects the PPM crates responsible for the Tile calorimeter, 32 TREX modules need to be installed. These modules are designed in such a way that they are simply plugged together with the PPMs on the backplane of the crate. Therefore, the LCD daughter-card has to be replaced by a passive module which only routes the signals to TREX. The tasks of the former LCD are taken over by four Data In-Out (DINO) FPGAs on TREX. These are Xilinx Artix-7 FPGAs which additionally duplicate the real-time data and send it to the main processing unit of TREX, the Preprocessor Data Collector (PREDATOR) FPGA.

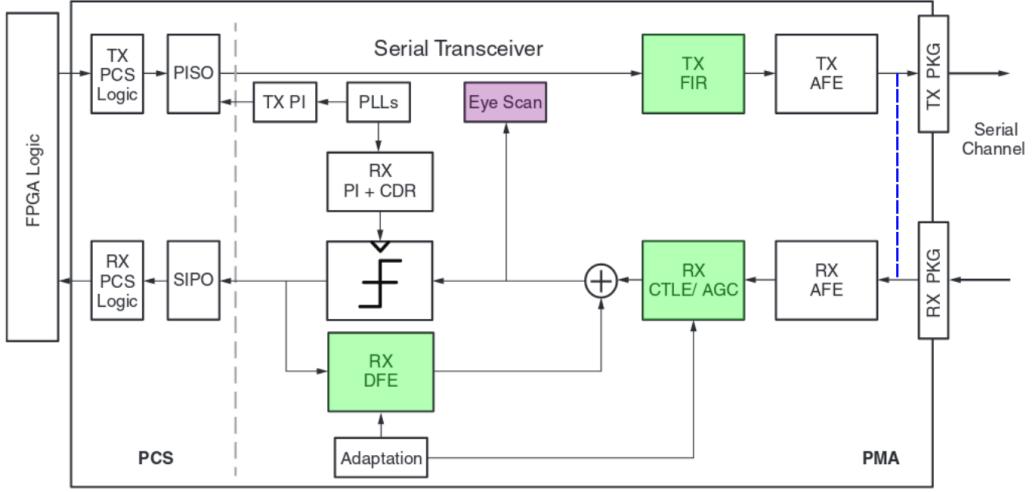

For the prototype, the PREDATOR is a Xilinx Kintex Ultrascale device with many intellectual property (IP) cores and 64 Gigabit transceivers of GTH series that can handle data rates up to 16.2 Gbps [17], whereas the agreement of data rates from TREX to FEXes is 11.2 Gbps. The final TREX version will use a smaller FPGA with less but still sufficient resources and only 56 GTHs, which is more than the maximum required number of 29 during operation. In the PREDATOR the incoming LVDS streams are at first deserialised and then demultiplexed in case of CP streams. LVDS start and stop bits as well as the parity bit are checked and discrepancies are reported to VME registers and FEXes via an error flag. Before optical transmission, the data is duplicated and formatted as required. Also parts of the readout functionality have to be moved from ReM to PREDATOR, since former readout

<sup>1</sup>Printed Circuit Board

**Figure 4.3:** Schematics of the TREX module. Real-time paths are marked in red and orange, VME paths in green and readout in blue. Passive LCD and ReM FPGA are components on the PPM. [11]

cards have to be removed to give TREX space. Board configuration works as for the PPM through VME. The connection is established via the CPLD and ReM FPGA for all TREX devices.

The slow control interface to the ATLAS DCS can't be implemented through the CAN module of the PPM because of insufficient physical connections between the modules. A commercial Zynq+ Multi-Processor System-on-Chip (MPSoC) device adopts this task for the TREX. It combines ARM<sup>2</sup> and FPGA architecture. Important information is gathered by Zynq and sent to the DCS via an Ethernet interface. The DCS is then able to power down the TREX separately or together with the PPM, since the power management of PPM and TREX are coupled. Note that the Zynq device is not part of the first TREX prototypes, but will be installed on future versions.

The opto-electrical conversion and their transmission is realised by Samtec FireFly devices. They achieve data rates up to 14.1 Gbps [28]. The board is equipped with four twelve-channel transmitters, where each is responsible for the transmission to one FEX, having one spare in case of defects to avoid module replacements. They are placed close to the PREDATOR on the PCB to keep track lengths short on the electrical high-speed connection. A duplex with four input and four output links is used to send event related data upon an L1A. On its input paths TTC signals are received. The readout interface in use after decommissioning of the legacy system is the Front-End Link EXchange (FELIX), which is in general the system between detector electronics and DAQ. In addition, a FireFly receiver is implemented only on the prototype for testing and debugging purposes of the optical transmission and is not foreseen for the final TREX version.

Apart from the main devices presented, smaller supplementary components are also installed on TREX. PLL<sup>3</sup> chips are used to generate low-jitter clocks as a reference for the Gigabit transceivers. Power Manager ICs<sup>4</sup> enable a safe activation and deactivation of the board and offer a hot-swap functionality to exchange it while under power. They allow further to implement a power sequence to switch on or off the various supply voltages in a fixed order, as recommended by the manufac-

<sup>2</sup>Advanced RISC Machine

<sup>3</sup>Phase-locked loop

<sup>4</sup>Integrated-circuit

turer. Together with the ADCs they are also used to monitor operating conditions, which is essential to guarantee safe operation. These components can provide environmental data for the slow-control functionality to DCS.

# Chapter 5

## TREX Functional Tests

After development of a prototype board the functionality of its single transmission steps have to be validated, as well as the verification of operating conditions within the specifications of the single devices. In the case of TREX three prototypes were fabricated and intensively tested in a laboratory environment. The setup contains an open VME crate equipped with a few fans, a VME crate controller and a PPM plus TREX in one crate slot. Additional components are added depending on the type of test. This chapter discusses the measurements of the operating conditions, the LVDS data reception in the PREDATOR FPGA, the validation of the optical transmission and a latency comparison of the former and upgraded Preprocessor system.

### 5.1 Monitoring of Operating Conditions

In order to make a statement about the reliability of TREX operation the operating parameters, i.e. temperatures, voltages and currents, have to be monitored and checked at best under final environmental or extreme conditions. Modern devices like FPGAs are equipped with on-chip sensors that translate the measured value into a digitised voltage and store it in a register. The simplest temperature sensor is for example a temperature-dependent resistance through which a little current is sent. The voltage drop over the resistance can then be converted into a temperature. Similar, currents are measured by the voltage drop they induce in a resistance. Connected with an ADC, the value can be read out via software.

In case of the PPM the amount of parameters is limited. There are 16 temperatures coming from the nMCMs and seven voltages, mainly supply voltages from VME backplane connectors or transformed voltages from DC/DC converters, to be monitored. With the TREX the amount is drastically extended. There are in total 14 temperature sensors on TREX. Each DINO FPGA, each Firefly, two power managers and two sensors on PREDATOR are available. 13 currents are measured indirectly and made accessible by two ADCs. The most important ones are currents from supply voltage pins in order to estimate the power consumption. The number of voltages captured with software tools was chosen to 44. Because of the large amount of components there are many possible voltage values which can be read by software, since some devices need multiple and different supply voltages. Even maximum and minimum long-term voltages are accessible. In the following, the monitored voltages are restricted to supply voltages. Thus, a sum of 94 values is recorded for PPM and TREX.

For the purpose of lab monitoring several applications were created with C++. The first application reads all the desired parameters via VME and writes them to log files as plain text on demand. While data taking the parameters of interest, grouped by temperatures, voltages or currents, are simultaneously displayed in the console. This division is made due to the large amount of parameters. The log

files are picked by a second application which presents them graphically by using ROOT. It creates single and summary plots grouped by boards, devices or quantities. In the end, one ROOT file is generated per measurement that stores all the related plots.

Another application compares actual measured values against definable thresholds. There are upper and lower thresholds for warning and error alarms, based on the device specifications. The limit range is narrower for warnings than for errors. A list of defined thresholds can be found in the appendix A. The outcome for each readout is also displayed in the console and written to log files. Warnings are reported and the operation continues, but in case of an error TREX is switched off by changing configuration bits in an I/O expander chip, that is connected to the power distribution of TREX. This can be undone via VME to power up TREX again.

For both applications, the total testing time and the readout period are configurable at start. The console outputs also indicate the current status of the measurements. But the reported values are not very meaningful in a first instance. The values seem to be rather arbitrary. In order to make them available in conventional dimensions transfer functions have to be applied. These functions are mainly provided by the manufacturer in the datasheet of the single device, as well as the register addresses of the parameters of interest. In case of the measured ADC values some additional factors have to be applied to consider previous voltage division or amplification steps. Also some data must be shifted or equivalently divided/multiplied, since not all provided bits in a register represent the measured value or two registers must be combined to a data word.. The transfer functions for TREX devices are summarised in table 5.1.

The results in the following sections make usage of the presented applications. They discuss the temperature development and power consumption at full load.

| Device                  | Quantity         | Data size   | Transfer Function                                                   |

|-------------------------|------------------|-------------|---------------------------------------------------------------------|

| Power Managers LTC2977  | Temperature [°C] | 16 bit      | $\tilde{b}[15 : 11] \cdot 2^{\tilde{b}[10:0]}$                      |

| Power Managers LTC2977  | Voltage [V]      | 16 bit      | $b \cdot 2^{-13}$ or $\tilde{b}[15 : 11] \cdot 2^{\tilde{b}[10:0]}$ |

| Samtec FireFlys         | Temperature [°C] | 8 bit       | $b$                                                                 |

| Samtec FireFlys         | Voltage [V]      | Twice 8 bit | $((b1 << 8) b2) \cdot 10^{-4}$                                      |

| DINO FPGAs              | Temperature [°C] | 16 bit      | $(b >> 4) \cdot \frac{503.975}{4096} - 273.15$                      |

| DINO FPGAs              | Voltage [V]      | 16 bit      | $(b >> 4)/4096 \cdot 3$                                             |

| PREDATOR FPGA           | Temperature [°C] | 16 bit      | $(b >> 6) \cdot \frac{501.3743}{1024} - 273.6777$                   |

| PREDATOR FPGA           | Voltage [V]      | 16 bit      | $b/65536 \cdot 3$                                                   |

| ADC MAX11615 & MAX11617 | Voltage [V]      | 11 bit      | $b \cdot V_D/2000$                                                  |

| ADC MAX11617            | Current [A]      | 11 bit      | $b/(2R \cdot Gain)$                                                 |

**Table 5.1:** Transfer functions for TREX devices. The symbol  $b$  stand for integer values of the device data in the given size. A tilde expresses a two's complement.  $R$  declares the resistance used for current measurements (2 or 5 mΩ) and  $Gain$  considers the amplification by an upstream operational amplifier (20 or 50).  $V_D$  is a voltage division factor (2 or 3) of down transformed voltages to fit the digitisation range of the ADCs [21], [24], [25], [29], [30], [32].

### 5.1.1 Temperature Development

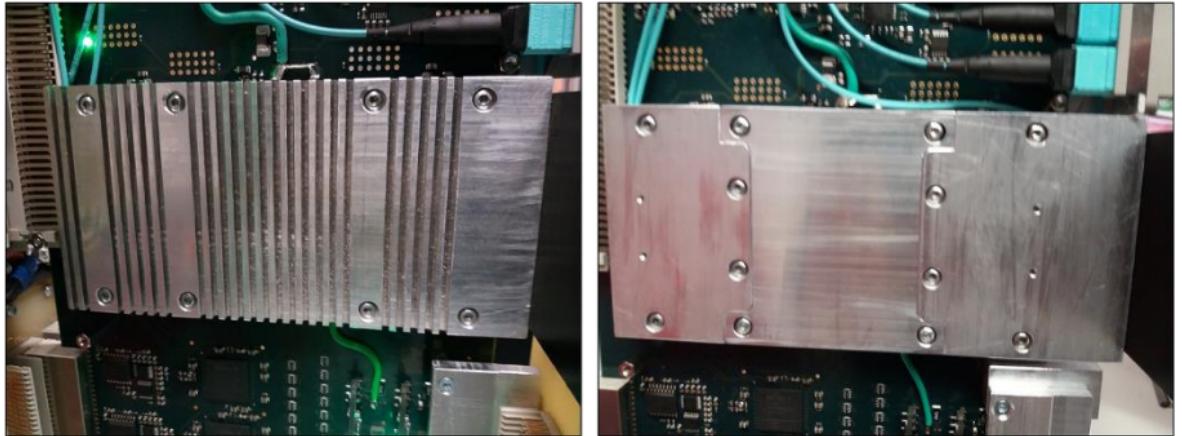

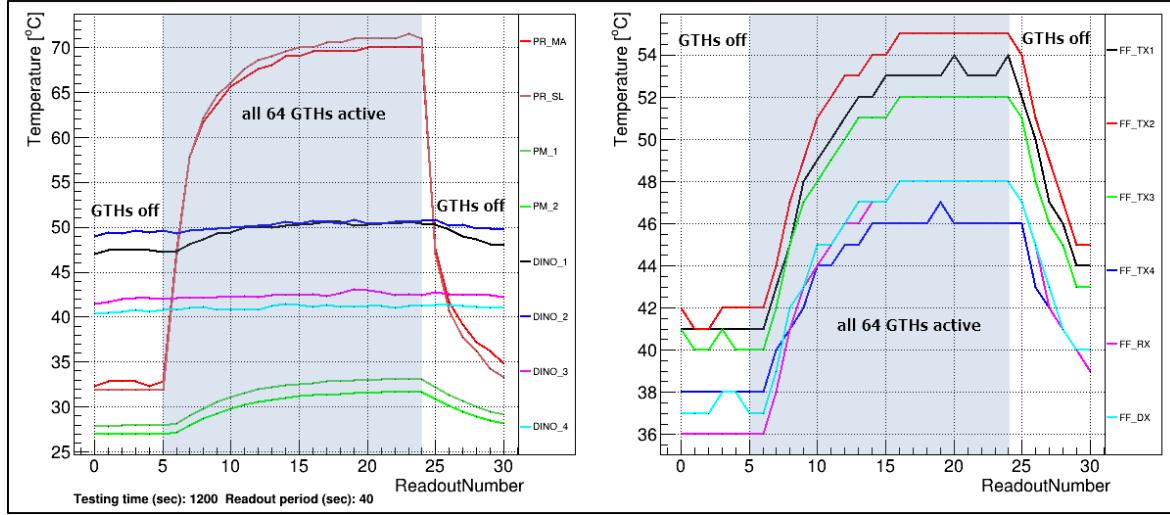

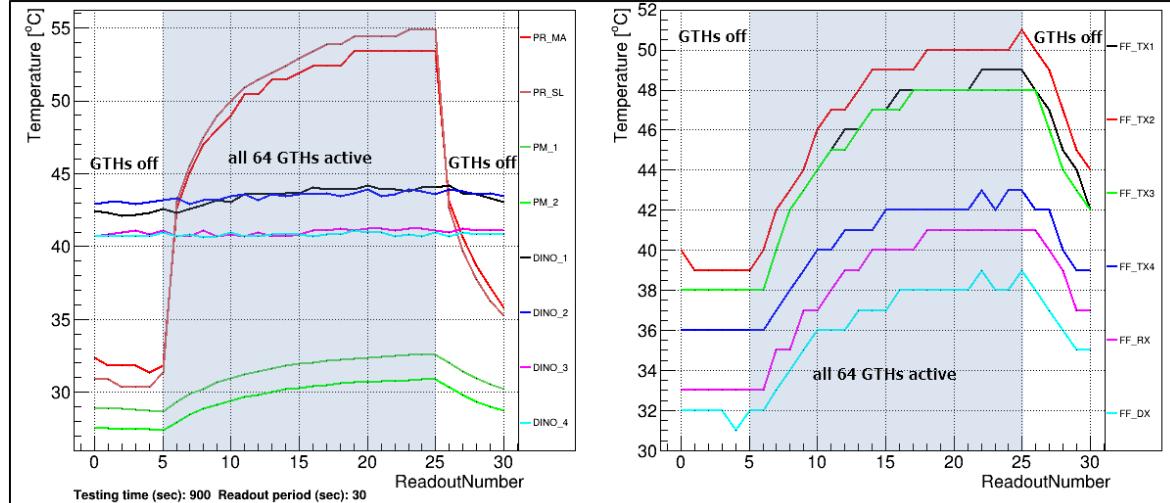

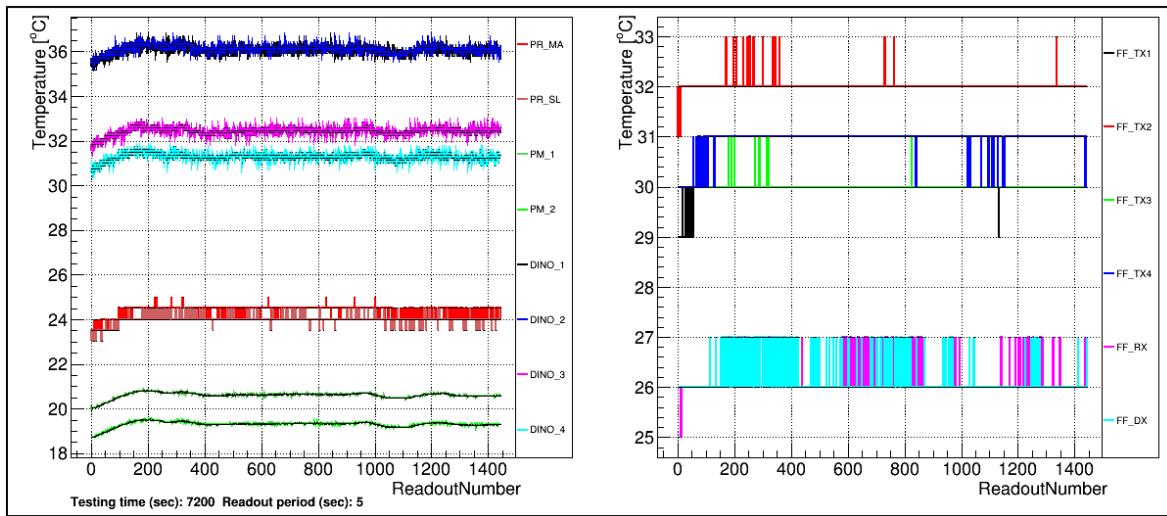

Heat generation during hardware operation is an unavoidable fact. To ensure a safe running and to avoid material damage, electronic installations need appropriate cooling. This is usually achieved by air- or water-cooling systems and heat sinks. A reference point for a safe temperature operating range is given by the manufacturer's specifications of the single devices. Xilinx recommends e.g. for the PREDATOR FPGA a range of 0-80°C [19]. In order to estimate possible critical heat developments, the board is operated at full load. The maximum possible consumption is simulated by enabling all 64 Gigabit transceivers of the PREDATOR FPGA and by sending stress patterns from the PPM playback memories. These stress patterns are an alternating series of logical 1s and 0s. The permanent toggling is a strain for the hardware. The Gigabit transceivers are very resource-intensive, so that 64 in simultaneous operation bring the PREDATOR FPGA to full use of the capacity. This happens in an open crate with a single occupied slot, equipped with provisional fans for all prototype modules at about 25°C room temperature. Additional heat sinks are mounted on top of the PREDATOR FPGA and FireFlys. Figure 5.1 shows the ones used in these tests. The first one is a monolithic corrugated body made of aluminium with a thermal conductive foil of 2mm thickness placed between the devices and body. The second one consist of three separated parts for a quick exchange of components and a 0.2mm thermal conductive foil. The test procedure is the following: the measurement starts with a cold board and a minimum configuration of the PREDATOR FPGA. After a few readouts the PREDATOR FPGA is reconfigured with all GTHs active. When the maximum temperature is reached the GTHs are again deactivated.

The results for the first heat sink are shown in figure 5.2. The effect of the GTHs is clearly visible by a sharp rise and fall of temperature when they are activated and deactivated. A maximum temperature of about 72 °C is reached on the PREDATOR FPGA and 55 °C for the FireFlys. The DINO FPGAs and the Power Managers seem to remain more or less stable or are only heated because of the material heat flow from PREDATOR. But 72 degrees are rather high compared to the device specification and the open environment. In a fully occupied crate, the inner boards will even be exposed to an increased heat generation due to the air binding and the surrounding boards. Thus, this heat removal may not be sufficient. The temperature development with the second heat sink is given in figure 5.3. It shows that the PREDATOR FPGA is approaching a maximum temperature of about 55 °C, while the hottest FireFly reaches 51 °C. The other temperature curves are similar to those of the previous measurement, whereat the upper DINO FPGAs are a little cooler. The second heat sinks thus offers a better heat dissipation. Note for both measurements that the temperature differences of the single FireFlys and

**Figure 5.1:** Heat sinks used on the TREX prototype modules. The left one is a single corrugated body. The right one consists of three separated parts.

**Figure 5.2:** TREX temperature monitoring with the first heat sink. It shows a 20 minutes measurement with a 40 second readout period. The left side shows the temperature development of the Power Mangers (PM) , the PREDATOR (PR) and the DINO FPGAS. The right side shows the temperature development of the FireFlys. The blue-shaded areas mark the time with 64 active Gigabit transceivers in the PREDATOR FPGA.

DINO FPGAs are related to the position and orientation of the provisional cooling.

While the first heat sink has a bigger surface area due to its shape, which is usually preferable, the second has a ten times thinner conductive thermal foil that allows a better heat transport from PREDATOR FPGA to the aluminium body. With this heat sink and an adequate air-cooling system it is guaranteed that TREX is able to operate in a safe temperature range. It should also be mentioned that Run-3 operation only requires 29 Gigabit transceivers to be simultaneous active. The heat generation on a single TREX board will therefore be lower compared to these tests.

**Figure 5.3:** TREX temperature monitoring with the second heat sink. It shows a 15 minutes measurement with a 30 second readout period. The left side shows the temperature development of the Power Mangers (PM) , the PREDATOR (PR) and the DINO FPGAS. The right side shows the temperature development of the FireFlys. The blue-shaded areas mark the time with 64 active Gigabit transceivers in the PREDATOR FPGA.

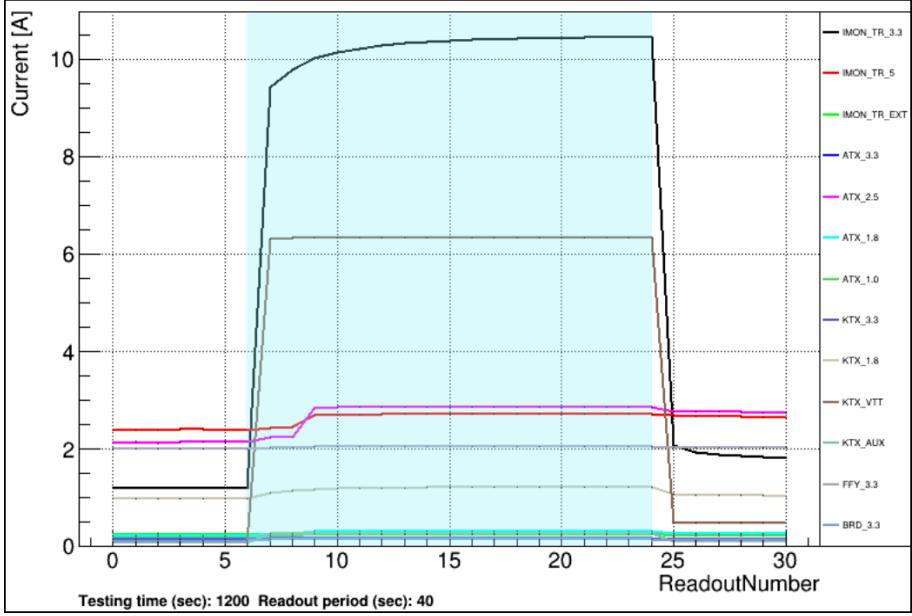

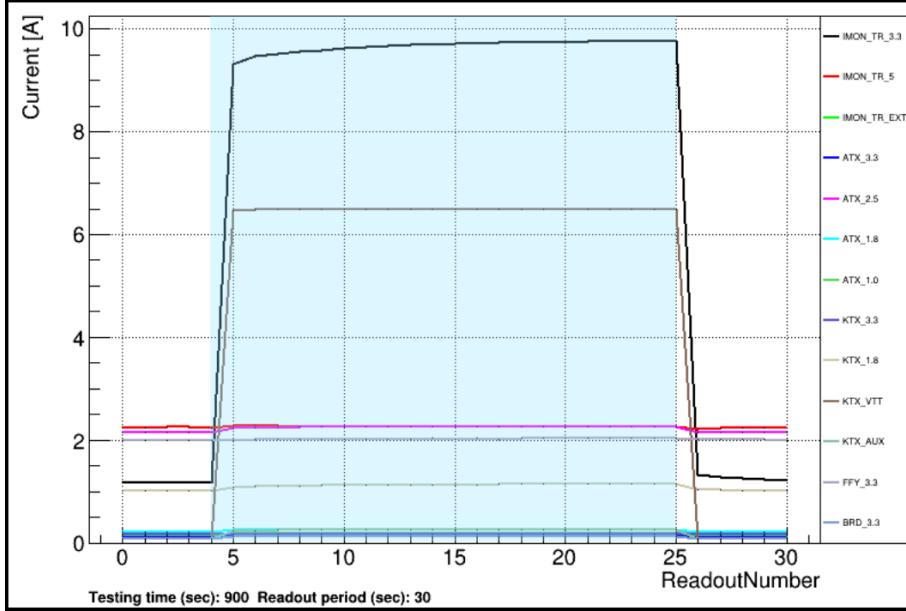

**Figure 5.4:** TREX current monitoring with the first heat sink. The black (IMON\\_TR\\_3.3) and red (IMON\\_TR\\_5) curve show currents from the +3.3V and +5V crate's power distribution. The others show various currents to supply pins of DINO (ATX) and PREDATOR (KTX) FPGAs or FireFlys (FFY). The blue-shaded areas mark the time with 64 active Gigabit transceivers in the PREDATOR FPGA.

### 5.1.2 Power Consumption

In general, power consumption is a key criterion for all electronic hardware. In the present case, TREX is ideally supplied by the same power supply unit as the PPM, since it represents its physical extension, although the possibility of an external supply is kept open. The current prototype is connected to the +3.3V and +5V power distribution lanes of the crate. These lanes provide up to 345A respectively. In Run-2, the PPMs consumed roughly 140A on the 3.3V supply and 160A on the 5V supply per crate [11]. Therefore, it has to be known whether the power demands of a single TREX exceeds the given limits of approximately 100W. This is checked under the some conditions like for the temperature. Current measurements for both heat sinks are shown in figures 5.4 and 5.5. The voltages are stable within their tolerance ranges, that is why the corresponding plots are not presented here. The main focus of both plots lies on the maximum currents of the power distributions. There is a clear increase in current with activation of the GTHs, mainly on the +3.3V distribution. The single current plots show that this trend is the same for all values, but with various characteristics. With the first heat sink the currents rise to approximately 10.5A on the +3.3V lane and 2.7A on the +5V lane, giving 48W of total power consumption. With the other heat sink these currents fall to 9.8A and 2.2A, resulting in 43W. This drop is explained by the temperature difference for both measurements. According to Matthiessen's rule the behaviour of the electrical resistivity of a conductor, in this case copper  $\rho_{\text{CU}}$ , can be split into a temperature-dependent  $\rho(T)$  and -independent part  $\rho_{\text{D}}$ :

$$\rho_{\text{CU}} = \rho(T) + \rho_{\text{D}}. \quad (5.1)$$

The constant term arises due to defects in the conductors crystal structure. The temperature dependence considers electron-phonon and electron-electron scattering processes, which are reduced at lower temperature [15]. A bigger resistance at higher temperature causes more losses in the board connections, that make the current increase for a still sufficient supply of the single devices. The sec-

**Figure 5.5:** TREX current monitoring with the second heat sink. The black (IMON\_TR\_3.3) and red (IMON\_TR\_5) curve show currents from the +3.3V and +5V crate's power distribution. The others show various currents to supply pins of DINO (ATX) and PREDATOR (KTX) FPGAs or FireFlys (FFY). The blue-shaded areas mark the time with 64 active Gigabit transceivers in the PREDATOR FPGA.

ond highest current in the plots, named KTX\_VTT, monitors the supply for the Gigabit transceivers. As expected, they ensure the highest current increase. The results show that TREX consumes less than half of the available power budget at full load. The operation with the same power supply like for the PPM should be safe. Nevertheless the balancing can be optimised. The power budget on the +3.3V lane is 42W per board, which is already reached in the upper measurements. On the other side, the +5V power budget is 58W per board. Some of the DC-DC converters on TREX, used for power distribution, offer the possibility to be supplied from either side. The connection is established by a solder bridge and can therefore be moved to other supply voltage pins. Also the supply of the Zynq+ device will be realised from the +5V distribution lane.

### 5.1.3 Operation in a new Environment

For test with other L1Calo submodules a TREX prototype has also been installed at CERN in a surface test facility (STF). The whole crate is placed inside of racks, together with the power supply unit and other hardware. The stable operation in this new environment has to be validated. For this reason TREX was monitored with the created application. Figure 5.6 shows the TREX temperature profile for a two hour measurement as a representative. All quantities stayed stable within their tolerances. Here, stress tests like in previous sections were omitted. The alarm application was running afterwards for about 26 hours. No errors or warnings occurred during this period, concluding TREX is running safely at STF. This test can be repeated with more logic or eventually the final firmware in the FPGAs.

**Figure 5.6:** TREX temperature monitoring at CERN STF. It shows a two hour measurement with a five second readout period. The jumps in FireFly temperatures are due to the resolution of the temperature sensor.

## 5.2 LVDS Data Reception and Alignment in PREDATOR FPGA

As explained in section 4.3, the real-time data of the nMCMs is duplicated on 48 physical links in the DINO FPGAs and send to PREDATOR. But the reception of this data has various timing on each link due to different signal path lengths and processing times in the DINO FPGAs or various routing through the PCB. This data has to be aligned on all links for a synchronous operation and correct BC-wise data selection.

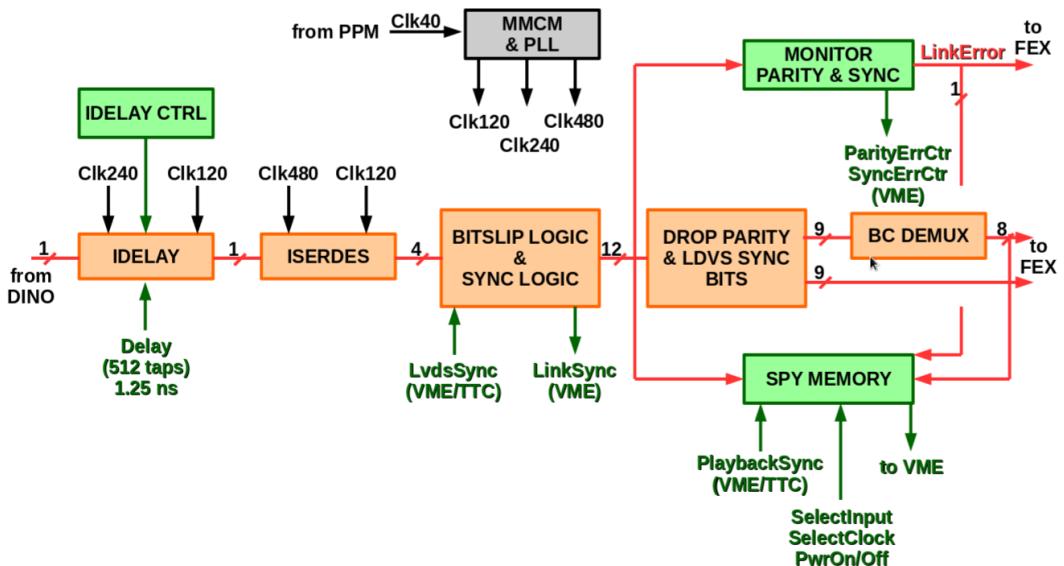

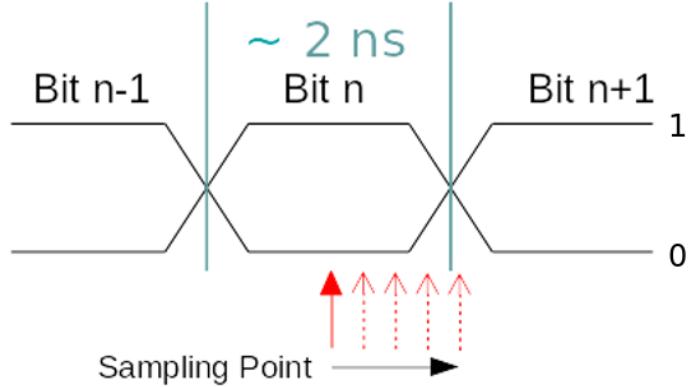

To check an error-free transmission and reception, the playback memories in the CALIPPR FPGAs are configured with known data. These memories start sending their contents on command. On PREDATOR side, these signals pass through several processing steps according to figure 5.7. At first, after conversion of the differential signals to single-ended form, they are send through a delay element called IDEALYE3. It is an Xilinx IP core and simply used for delaying signals by shifting the sampling point at the next input stage like figure 5.8 illustrates. ISERDESE3 is another IP core responsible for the parallelisation of the incoming serial streams in packages of four bits. How to pick and combine these packages to the original twelve bit word is decided by the bitslip and synchronisation logic. When setting up the board, various commands are sent to the single devices. The PREDATOR receives synchronisation commands, whereas the nMCMs send training patterns to the bitslip logic. Since the LVDS frame bits are always a logical 1 at the beginning and a logical 0 at the end of the data word, these training patterns are a series of six consecutive 1s and six consecutive 0s. The receiving logic recomposes the incoming bits to this pattern and locks its final decision for future operation.

After this stage, the recombined data is monitored by calculating and comparing the parity bit and checking synchronisation. In case of former CP data, the streams are additionally demultiplexed before further processing and preparation for optical transmission occurs. The received data can also be transferred to a SPY memory for testing purposes. These are 18-bit wide memories with 1024 registers on each transmission channel. At the end, those entries are read via VME and compared to the data that has been sent.

To emulate the processing the data undergoes on its way to PREDATOR, dedicated software functions are used to make playback and SPY data comparable. On CALIPPR side, single logical blocks can be bypassed for simplicity of these tests. Also the synchronisation FIFO, the FIR filter and the pedestal

**Figure 5.7:** LVDS data input to PREDATOR FPGA. IDELAY, IDEALYCTRL and ISERDES are Xilinx IP cores. Components in green are for configuration and monitoring, while orange elements indicate real-time processing steps [27].

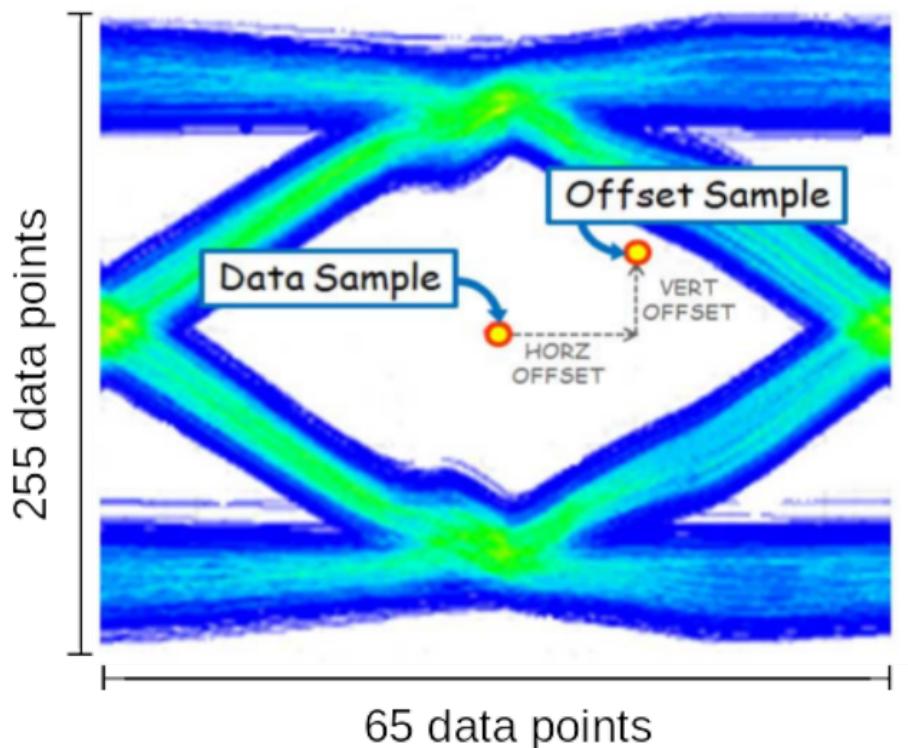

**Figure 5.8:** Sketch of IDELAYE3 functionality. Logical levels are indicated on the right side. Single bits are depicted as eye diagrams. IDELAYE3 shifts the point in time when incoming signals get sampled. At this stage, transmission occurs at 480 Mbps that correspond to a bit length of 2.083ns.

correction can be configured for an effectless routing of the playback data (compare figure 3.4). The LUT, the BCID decision logic, the BC-multiplexing and the packing of the parity bit can be bypassed for CP links, so that the pure playback data is received by PREDATOR. This does not hold for JEP links. Here, only the bit truncation as well as the parity packing can be bypassed. The simulation can be configured to consider this different processing.

### 5.2.1 Characterisation of IDELAYE3

Although the functionality of the IDELAYE3 is already known, there are a few characteristics that have to be determined. In general, this component is a 512 tap delay line that offers the possibility for a calibrated time delay with voltage and temperature compensation [22]. This built-in-self-calibration (BISC) process runs permanently in the background and is also responsible for an initial non-zero delay tap value, even if no delay applied, that wants to compensate internal skews between clock and data insertion at the first capturing flip-flops of ISERDESE3. These skews appear because of different routing of clock and data in the FPGA. Typically, the outcome is a tap value between 45 and 65 which is called ALIGN DELAY. An IDELAYCTRL component must be instantiated to make this happen. The resolution of a single tap is given by 2.5 to 15 ps [19], ending up with total delays of 1.28 to 7.68 ns. The exact value is also connected to the reference clock of the IDELAYCTRL, but explanations how to adjust the clock for different tap sizes are missing. Nevertheless, the tap resolution and with it the overall delay can be determined [18]. When instantiating the IDELAYE3 component in the firmware, certain attributes have to be set. One of these is an initial DELAY VALUE in the range of 0 - 1250 ps. If it is non-zero, the resulting tap number will be bigger than the ALIGN DELAY. Thus, two firmware version with different DELAY VALUES  $d_1 > d_0$  are created and the corresponding tap numbers  $n_1$  and  $n_0$  are read via VME. The tap size resolution  $t_{\text{res}}$  can then be calculated according to

$$t_{\text{res}} = \frac{d_1 - d_0}{n_1 - n_0}. \quad (5.2)$$

Doing this with even more firmware versions, average resolutions of 4.35 - 4.46 ps for different links are calculated. This gives a total delay of 2.22 - 2.28 ns for the whole delay line. With the given transmission rates of 480 Mbps at this stage, the IDELAYE3 component is therefore able to delay incoming signals by more than a bit length. The exact numbers may vary with different boards but they should be comparable.

### 5.2.2 Test Procedure

The precise insight of the reception process is crucial for the avoidance of incorrect sampling. Signal sampling during the transition between logical levels, corresponding to the line crossings in figure 5.8, leads to transmission errors because the logical state is not clearly defined in this period. The fine-tuning of the sampling point must therefore be carried out on each receiving system. With the use of the introduced delay component two things have to be determined:

- 1) valid delay tap ranges.

- 2) the stability of a fixed delay.

The idea is simply to send data from the playback memories, store it in SPY and search for transmission errors in data and LVDS frame bits. This is repeated for each delay tap or for a fixed delay over a configurable period of time and controlled from software. The results are presented in histograms. Because of the different bypass options for CP and JEP links, different playback patterns, that means the series of transmitted data from the playback memory to PREDATOR, are used on the respective links. On CP side either a constant pattern, as for the synchronisation of the receiving logic on PREDATOR, or a ramp pattern with increasing numbers is sent, that provokes a more stressful transmission. The pattern used on JEP side is a series of growing pulses in increment steps of four with a zero as every second entry, since the Peak Finder algorithm only permits a non-zero data transmission at every second bunch-crossing. The decision in favour of four-increments was made because the sequence of LUT and channel summations is effectively truncating the two least significant bits of the 10-bit data word in the applied bypass configuration of the CALIPPR FPGA. This effect is not considered in the existing simulation software.

All patterns start with an unique identifier that flags the beginning of the receiving data in the SPY memory. Activation of SPY and the start of playback transmission can not be controlled from software in perfect timing. The first registers of SPY will be therefore filled with some dummy values at these tests. But since the SPY exceeds the playback in size by a factor of four, the whole playback pattern is at least three times completely contained in SPY. Finally, to make a statement about the alignment of data, the register addresses of the unique identifier will be compared to each other on all links. To cover all receiving logic, a extended version of this test application checks the BC demultiplexing and those alignment in the same manner.

### 5.2.3 Delay Scans

As explained, the first tasks is the determination of valid delay tap ranges. The software processes the following sequence: set a delay tap number, synchronise the receiving logic, enable playback transmission, read the received data for analysis and start all over with an increased delay tap number. The data is thereby sent in packages of twelve bits. Ten bits are playback data while the other two are the LVDS frame bits. Errors in data and LVDS frame transmission are treated separately for analysis in the first instance. But observations revealed the same error tendency, which is why histograms with the combined results are created. Since the playback pattern is checked up to three times in SPY, the maximum number of errors is 768 for data and LVDS frame bits respectively. If the application is unable to detect the unique identifier, the number of combined errors is set to a maximum of 2048, twice the register size of SPY.

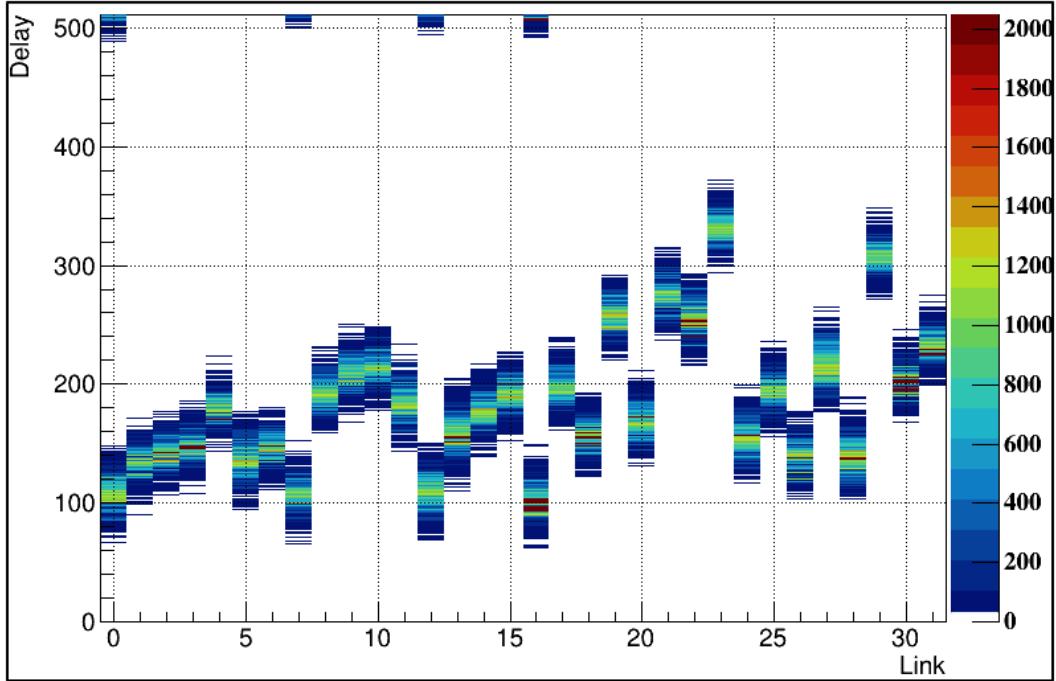

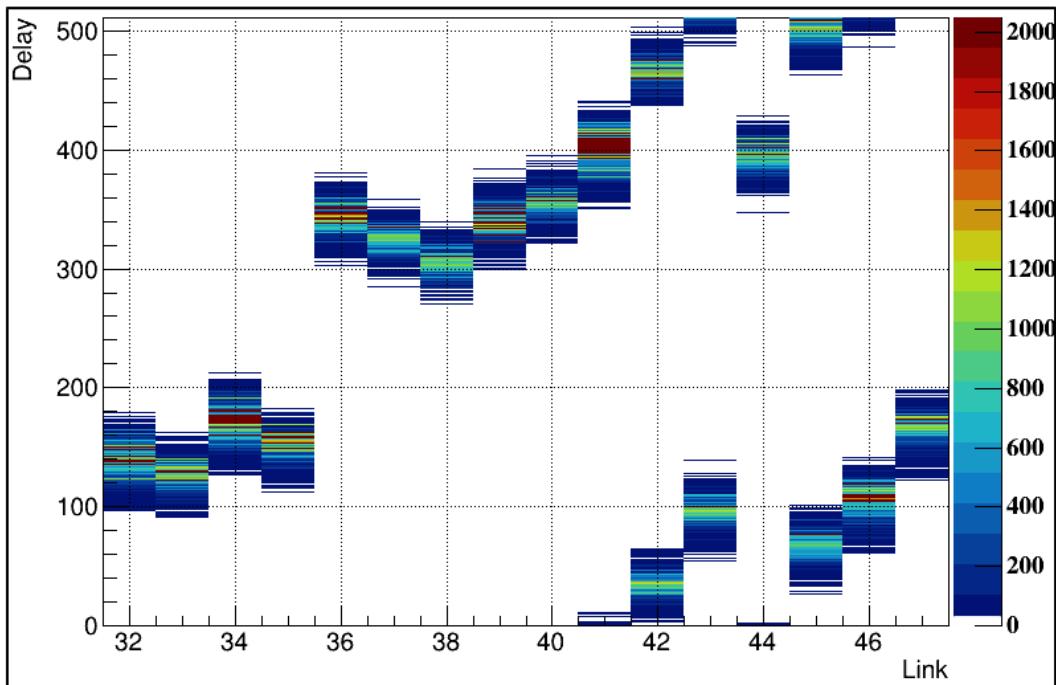

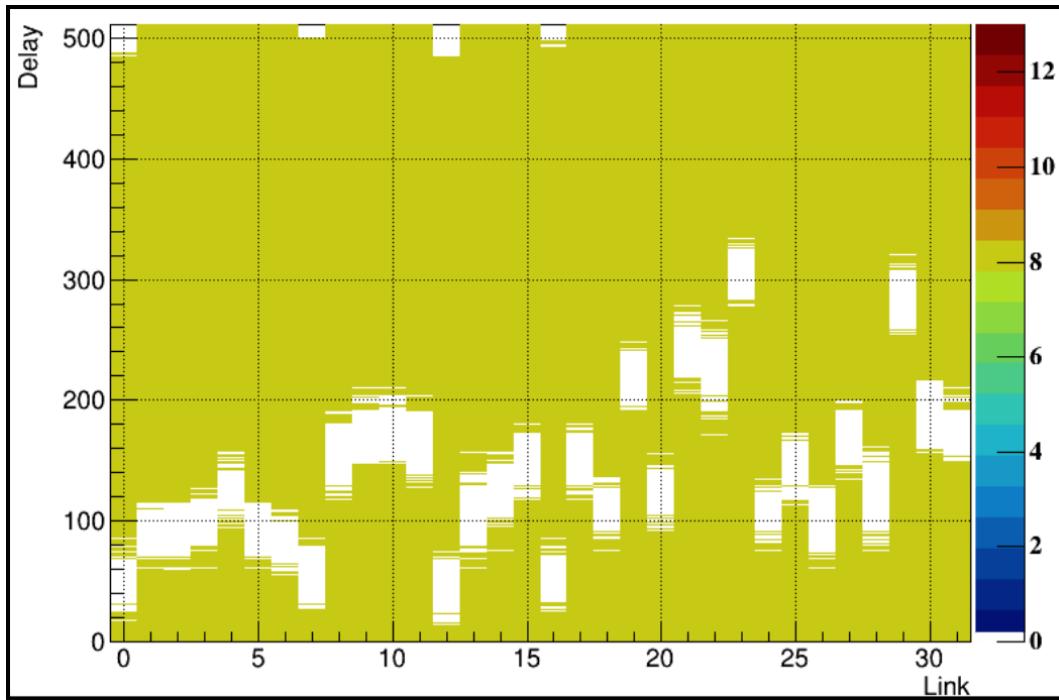

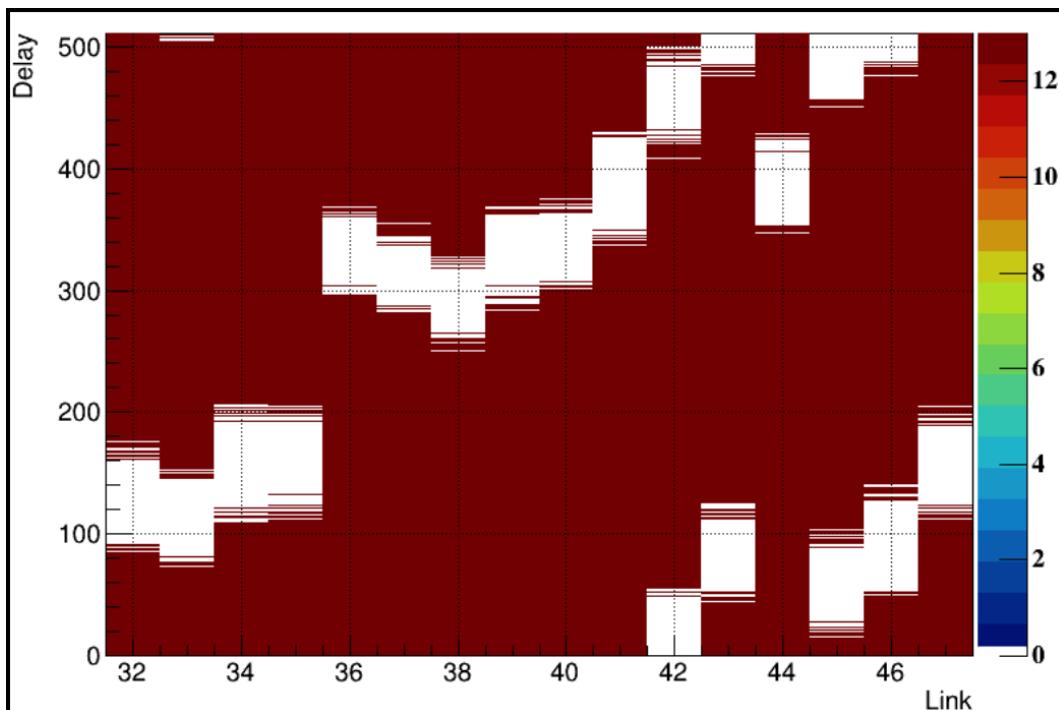

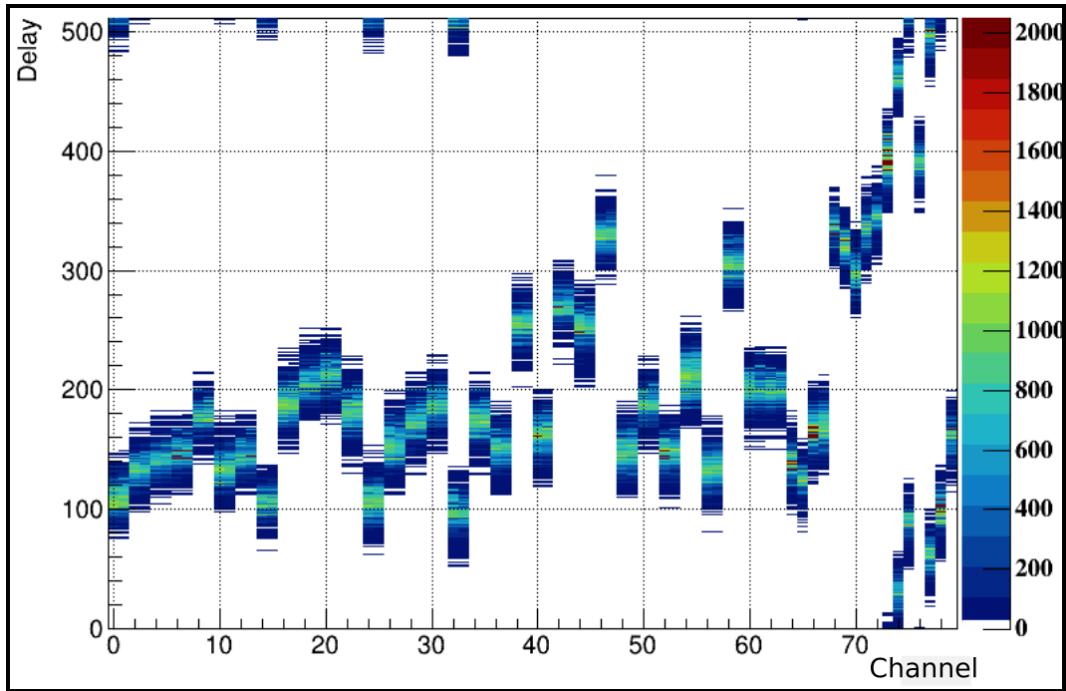

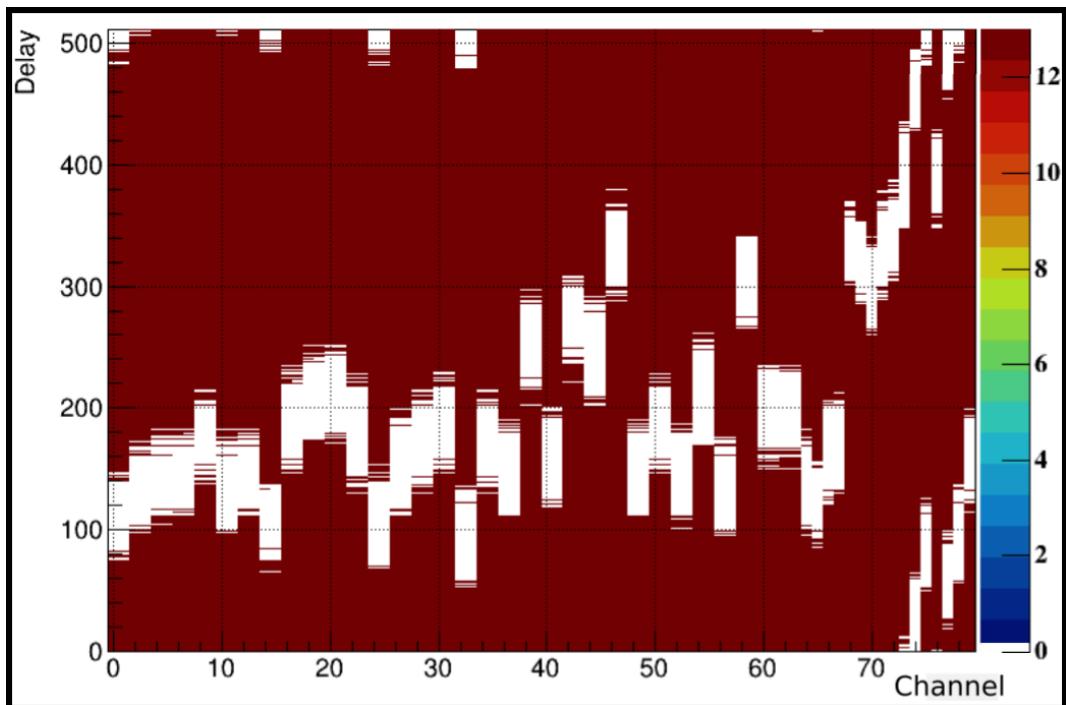

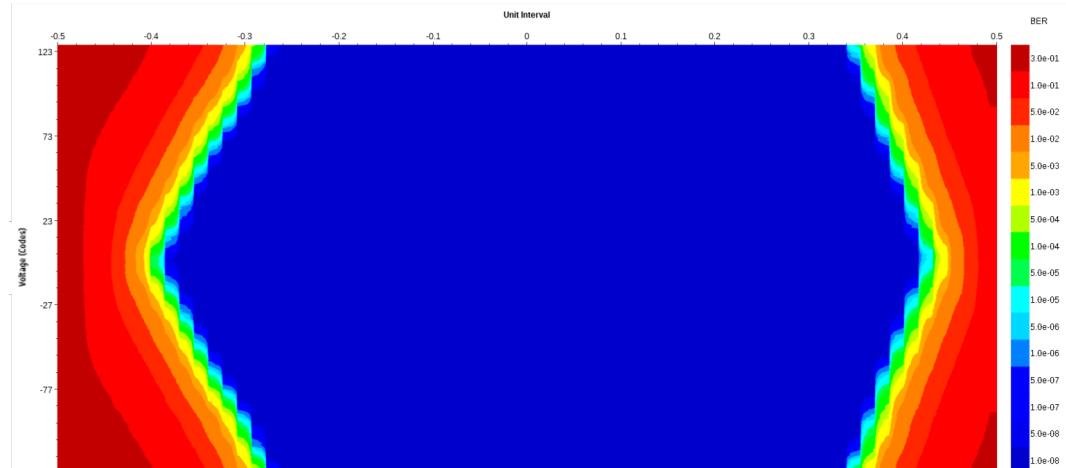

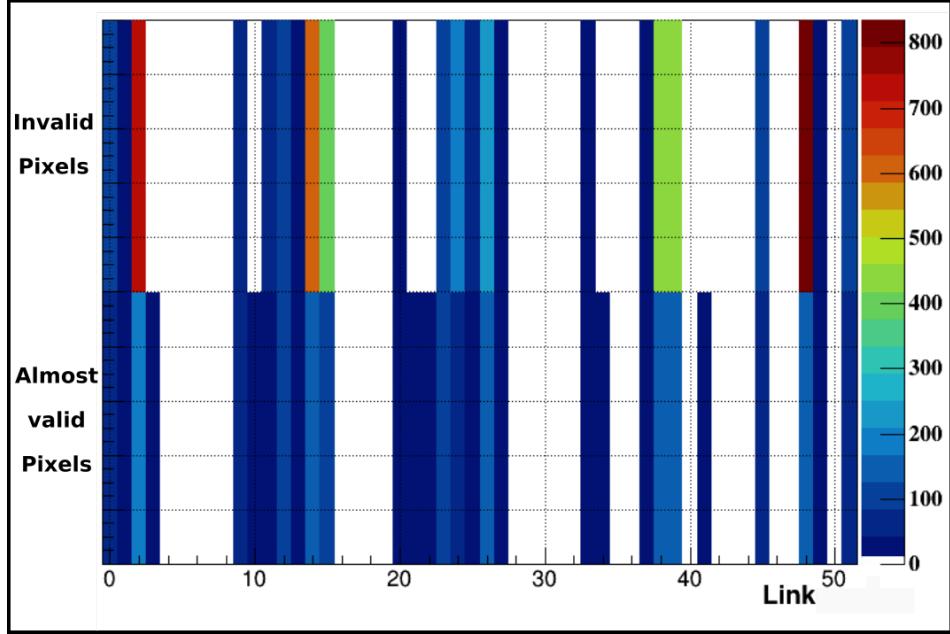

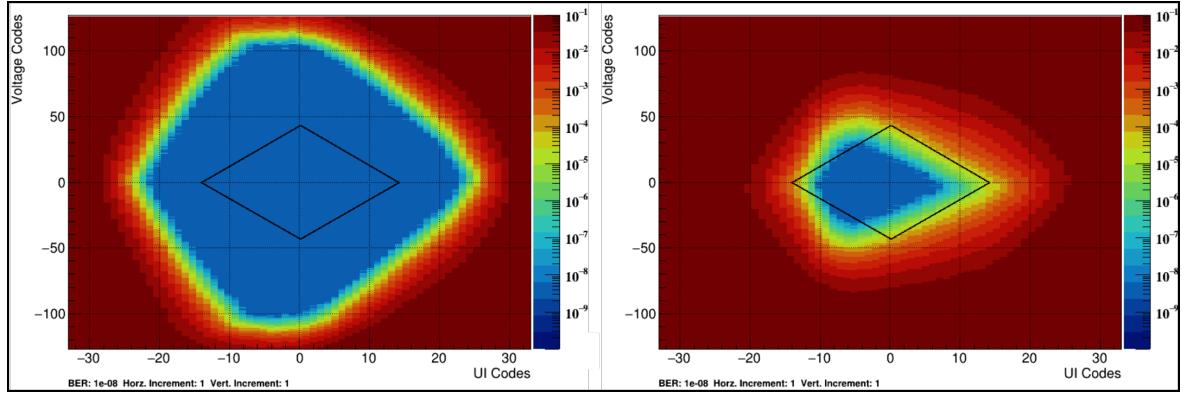

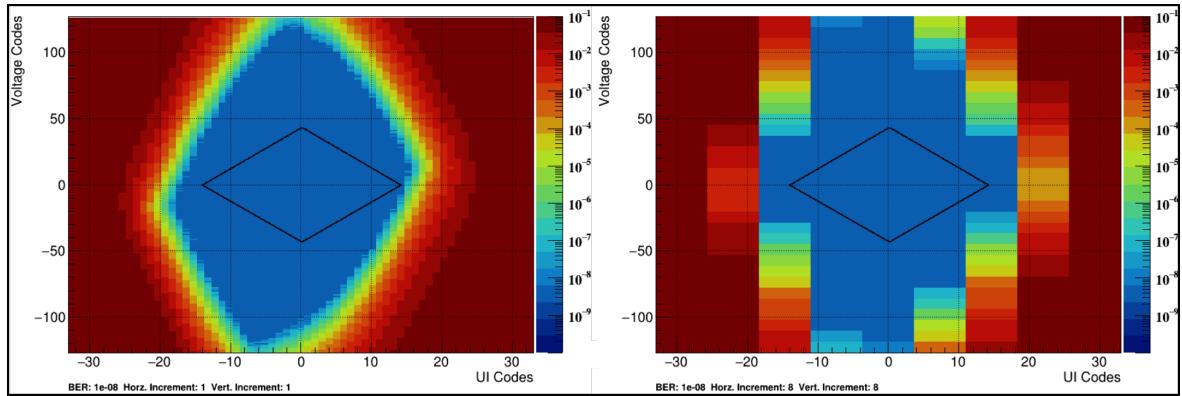

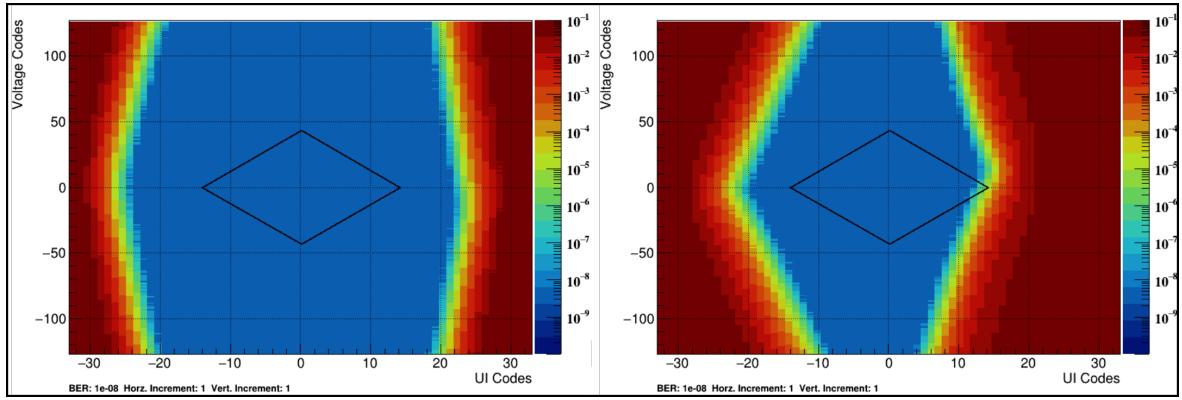

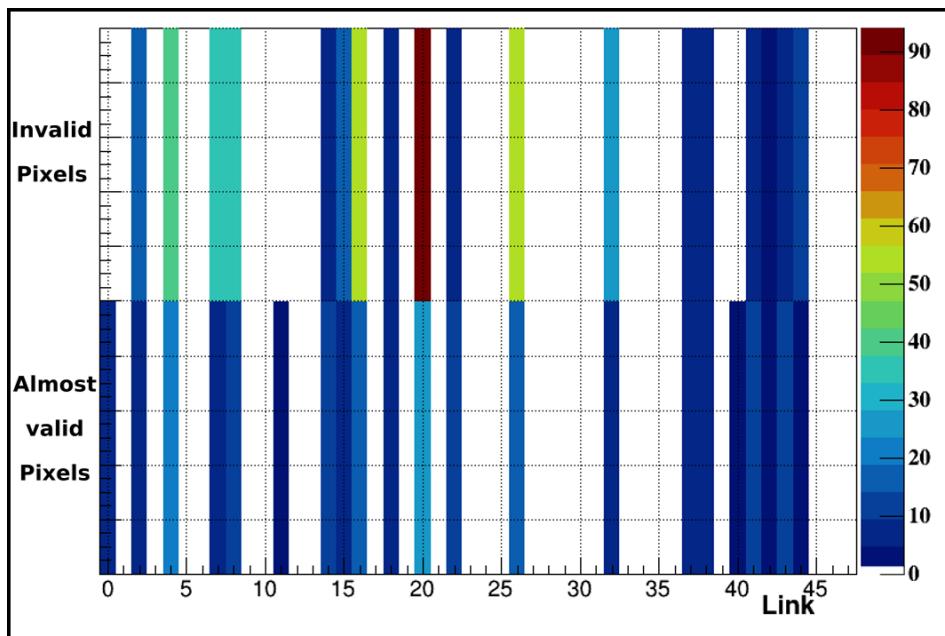

The resulting histograms are presented in figures 5.9 and 5.10. Link numbers up to 31 stand for CP connections, higher numbers for JEP connections. The results can be interpreted in analogy to eye diagrams. These diagrams are usually recorded with an oscilloscope, showing the overlay of the same

**Figure 5.9:** Delay scan for CP links. The link number is plotted against the delay tap number of IDELAYE3. Colours indicate the amount of detected transmission errors for a given delay tap. White areas stand for correct transmission.

**Figure 5.10:** Delay scan for JEP links. The link number is plotted against the delay tap number of IDELAYE3. Colours indicate the amount of detected transmission errors for a given delay tap. White areas stand for correct transmission.

digital signal for different points in time. Coloured areas, indicating transmission errors, correspond to the eye margins where transitions of logical levels take place. They also demonstrate nicely by the colour changes that the transmission errors increase towards the middle of these regions. This is conform to an increased intersymbol interference because of the closure at eye margins.

Some links also show the beginning of a second eye margin. This reassures the characterisation of the delay element and the determined total delay. The results vary slightly with the used playback pattern. A more stressful pattern like the ramp broadens the error ranges in comparison to a constant one. But the positions in the histograms stay the same. The results are in good agreement with all TREX prototypes while using the same PPM. Only very slight shifts in the invalid delay ranges were observed, whereat the overall arrangement was the same on all TREXes. These shifts are most likely caused by manufacturing tolerances of the PCB.

The histograms clarify that there are enough valid delay taps that allow a safe sampling of receiving data in PREDATOR. Ideally, sampling takes place in the middle of an eye. Converted to a delay tap number this would be e.g. approximately 320 for link 0. But to assess whether a once configured delay is stable and safe enough for operation, a long-term test must be performed.

#### 5.2.4 Stability of Valid Delays