**Department of Physics and Astronomy

Heidelberg University**

Masters thesis

in Physics

submitted by

**Niccolò Rigi-Luperti**

born in Tübingen

2024

---

# Readout-Circuits for Superconducting Nanowire Single Photon Detectors

*Advisor:* Prof. Dr. Wolfram Pernice

*Second advisor:* Dr. Simone Ferrari

# Abstract

Superconducting Nanowire Single Photon Detectors (SNSPDs) provide high detection efficiencies and fast count rates over a broad wavelength range, leading to their use in many high performance applications. Due to their operation at cryogenic temperatures, readout via electrical wires is limited in scalability due to the wires' thermal load. An alternative interfacing strategy is provided by optical readout, which could offer lower thermal load and higher data transfer bandwidths via optical fiber interconnects.

To this end, I investigate in this thesis new possibilities of interfacing SNSPDs with electro-optic-modulators such that the SNSPDs voltage signals could be registered via optical readout. I propose and investigate three new interfacing circuits, which give rise to output voltages two orders of magnitude larger than reported for similar previous circuits, reaching the required voltage threshold for optical readout.

As a second part of this thesis, I set up a basis to conduct cryogenic heat transport simulations and present an interfacing circuit that incorporates a self-regulated electro-thermal switch. Finally, I fabricate and measure integrated chips to extract resistances of cryogenic thin-film resistors and critical currents of thin-film superconducting devices.

# Contents

|                 |                                                            |           |

|-----------------|------------------------------------------------------------|-----------|

| <b>Abstract</b> | <b>i</b>                                                   |           |

| <b>1</b>        | <b>Introduction</b>                                        | <b>1</b>  |

| 1.1             | Motivation for this thesis . . . . .                       | 1         |

| 1.2             | This thesis work . . . . .                                 | 2         |

| <b>2</b>        | <b>Background</b>                                          | <b>3</b>  |

| 2.1             | Superconducting Nanowire Single Photon Detectors . . . . . | 3         |

| 2.1.1           | Basics . . . . .                                           | 3         |

| 2.1.2           | Integration on-chip . . . . .                              | 4         |

| 2.1.3           | History . . . . .                                          | 5         |

| 2.1.4           | Detection mechanism . . . . .                              | 6         |

| 2.1.5           | Fundamental properties . . . . .                           | 7         |

| 2.1.6           | Circuit dynamics . . . . .                                 | 11        |

| 2.1.7           | Latching . . . . .                                         | 13        |

| 2.1.8           | Further details . . . . .                                  | 14        |

| 2.2             | Intermediate signal amplification . . . . .                | 14        |

| 2.3             | Readout of SNSPDs . . . . .                                | 18        |

| 2.3.1           | Electronic readout . . . . .                               | 19        |

| 2.3.2           | Optical readout . . . . .                                  | 20        |

| <b>3</b>        | <b>Simulating a cryogenic thermal switch</b>               | <b>24</b> |

| 3.1             | Simulation tool . . . . .                                  | 24        |

| 3.2             | Material properties at cryogenic temperatures . . . . .    | 25        |

| 3.2.1           | Heat capacities . . . . .                                  | 27        |

| 3.2.2           | Thermal conductivities . . . . .                           | 28        |

| 3.2.3           | Thermal boundary conductances . . . . .                    | 30        |

| 3.2.4           | Thin film electrical resistivities . . . . .               | 31        |

| 3.3             | Geometry and Boundary Conditions . . . . .                 | 32        |

| 3.4             | Results . . . . .                                          | 34        |

| 3.5             | Conclusion of Chapter 3 . . . . .                          | 40        |

| <b>4</b>        | <b>Investigating new superconducting readout-circuits</b>  | <b>42</b> |

| 4.1             | Simulation tool . . . . .                                  | 43        |

| 4.2             | Heuristics that guided circuit design . . . . .            | 45        |

|                         |                                                                         |           |

|-------------------------|-------------------------------------------------------------------------|-----------|

| 4.3                     | Circuit 1: Voltage amplification via a highly-resistive SNSPD . . . . . | 46        |

| 4.4                     | Circuit 2: Voltage amplification via cascading . . . . .                | 51        |

| 4.5                     | Circuit 3: Voltage amplification via a thermal switch . . . . .         | 53        |

| 4.6                     | Conclusion of Chapter 4 . . . . .                                       | 58        |

| <b>5</b>                | <b>Experiments</b>                                                      | <b>60</b> |

| 5.1                     | Experimental Methods . . . . .                                          | 60        |

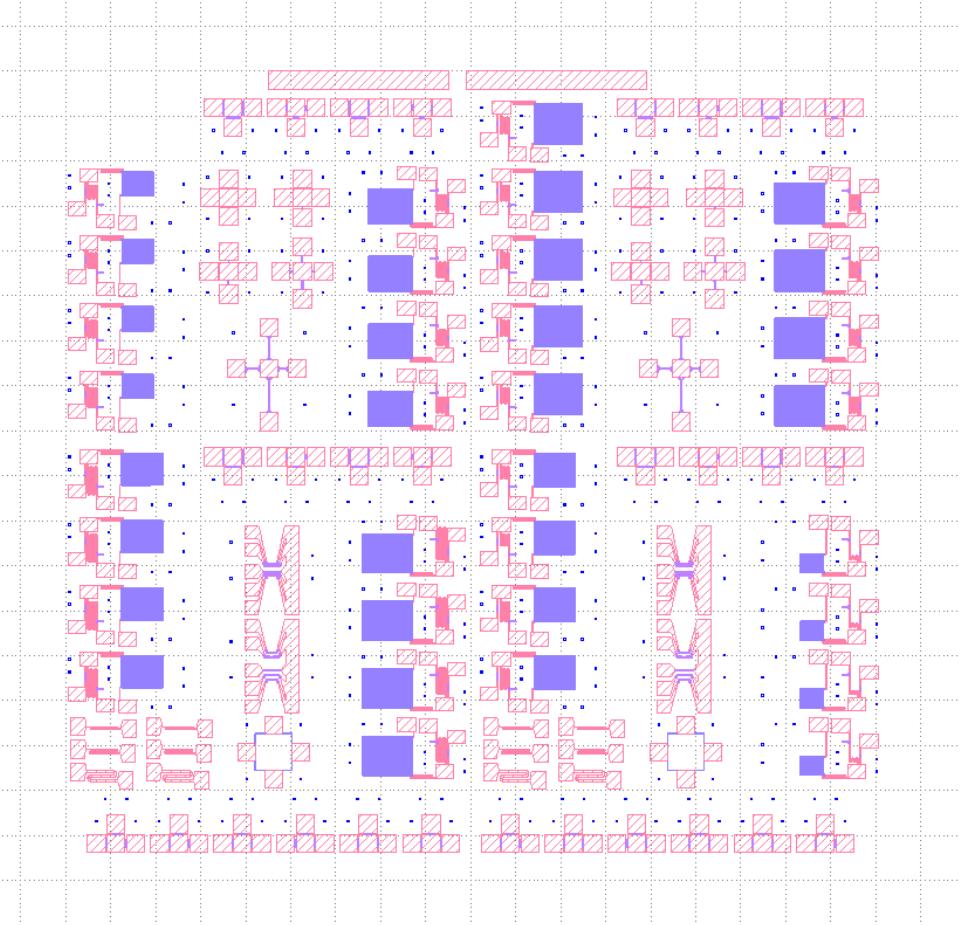

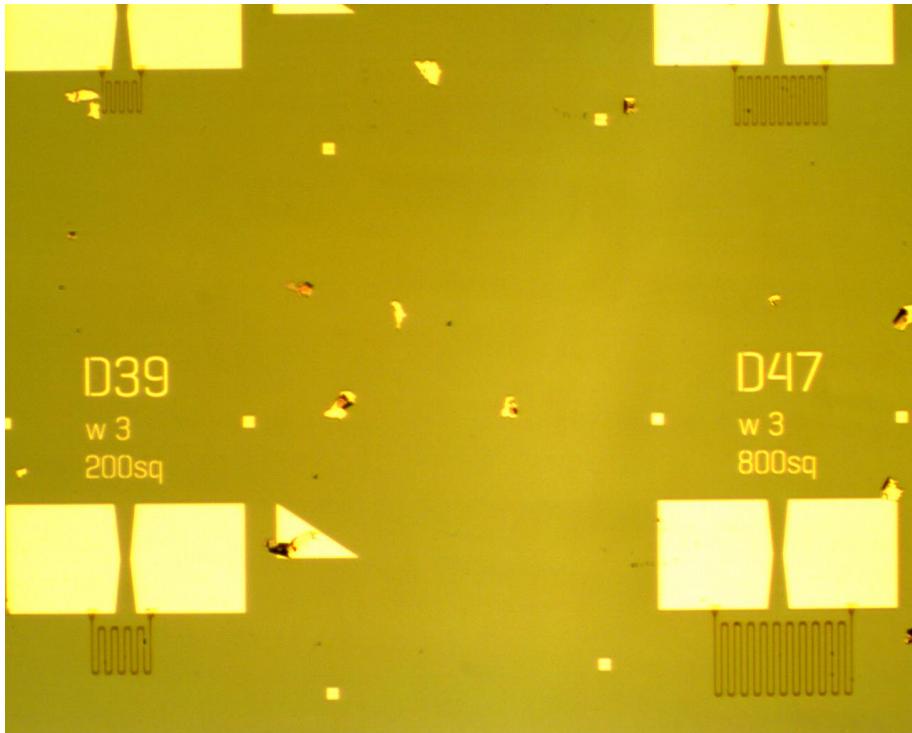

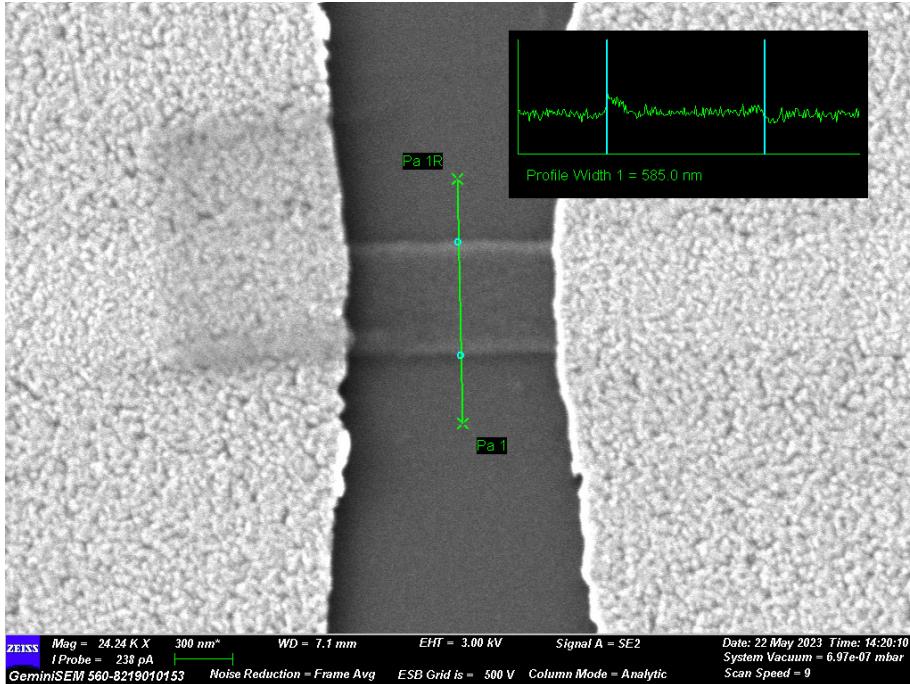

| 5.2                     | Fabricated Chips . . . . .                                              | 68        |

| 5.3                     | Results . . . . .                                                       | 70        |

| 5.4                     | Conclusion of Chapter 5 . . . . .                                       | 76        |

| <b>6</b>                | <b>Conclusion</b>                                                       | <b>77</b> |

| <b>Acknowledgements</b> |                                                                         | <b>79</b> |

| <b>Appendix</b>         |                                                                         | <b>80</b> |

| <b>Bibliography</b>     |                                                                         | <b>83</b> |

# Chapter 1

## Introduction

### 1.1 Motivation for this thesis

Detecting weak optical signals is of importance in a multitude of fields, e.g. communication [1], sensing [2], attempts at quantum computing [3] and fundamental physics [4]. Some examples include medical fluorescence imaging [5], metrology of fundamental quantum states [6], deep-UV astronomy [7] and space communication [8].

To this end, Superconducting Nanowire Single Photon Detectors (SNSPDs) are a class of photodetectors that are able to detect light down to the single-photon level upon local suppression of the superconducting state due to photon absorption. This high sensitivity to single photons makes SNSPD especially useful for applications where high detection performance is required [9].

A growing field of research is integrated photonics [10], where light is guided and manipulated within single chips. Fabrication of such photonic chips is done via lithographic methods starting with initial wafers, which offer excellent spatial resolution down to the nm-level and high reproducibility.

SNSPDs can be integrated in such a photonic chips, tailoring their performance towards e.g. high count rates [11], low dark-counts [12], low jitter [13] and high detection efficiencies at broad wavelengths [14]. Compared to semiconductor-based photodetection, SNSPDs are especially competitive in the infrared (IR) and ultraviolet (UV) regimes [15].

The high integration density of SNSPDs motivates research also in the design of large detector-arrays, where thousands of detectors are integrated on a single chip in array-like fashion. Further scaling could allow such arrays of detectors to be used as cameras, especially for the UV and IR, with promising recent proof-of-concept demonstrations [16].

SNSPDs need to be operated at cryogenic temperatures in the range of 1-4K, requiring cryogenic systems. Each wire that is connected to such a cryogenic device introduces a thermal load. This limits the achievable number of simultaneously addressable devices to and from such a chip due to the limited cryogenic cooling power [17].

To improve on this limitation in multi-device addressability, research has been growing in the study of optical readout[18]. Hereby, on-chip electro-optic modulators (EOMs) link

electrical to optical signals, allowing to interface a cryogenic chip optically instead of with wires [19].

Using optical fibers to carry information from the cryogenic to the room-temperature world could allow for lower thermal load and higher data throughput, leveraging techniques such as wavelength division multiplexing [20]. This would be especially useful for densely-integrated chips. In aforementioned large-detector arrays, optical fibers could allow to address multiple detectors at the same time, which currently with electrical wires is not possible [21].

Optical readout of SNSPDs is a rather recent field of research, with first experimental demonstration by Cea et al. in 2020 [22]. In their setup, the detection was limited to UV photons and the the maximum photon count rate (on the order of 1MHz) was mainly limited by the reset time of the EOM.

## 1.2 This thesis work

In this thesis, I investigate whether optical readout of SNSPDs can be extended into the IR-sensitive regime and whether interfacing them with a different EOM design can result in shorter reset times.

To this end, I designed and analysed three new superconducting circuits that could interface a waveguide-integrated IR-sensitive SNSPD with an integrated-photonics-based  $\text{LiNb}_3$ -EOM, such that the generated optical modulation would be strong enough for optical readout.

These three interfacing circuits are reported in Chapter 3 and constitute the main work of this thesis.

In one of these circuit a thermal switch was included. Simulating its thermal properties at cryogenic temperatures grew into it's own Chapter, Chapter 2.

Finally in Chapter 4, I show three fabricated chips and characterize them, to test the performance of the proposed circuit components.

# Chapter 2

## Background

This first chapter is intended to give background knowledge to all the topics that are of relevance for this thesis. I first introduce SNSPDs and will then discuss strategies how their detection signal can be amplified and read out.

### 2.1 Superconducting Nanowire Single Photon Detectors

Superconducting Nanowire Single Photon Detectors (SNSPDs) are a specific class of photodetectors with allow to detect single photons. I introduce here first their general properties, their history, and the detection mechanism. Then I introduce four fundamental properties of an SNSPD. With these, one can describe it's most basic equivalent electrical model. I finish by showing a basic interfacing circuit and discuss the detection cycle and some resulting basic requirements on the circuit design.

#### 2.1.1 Basics

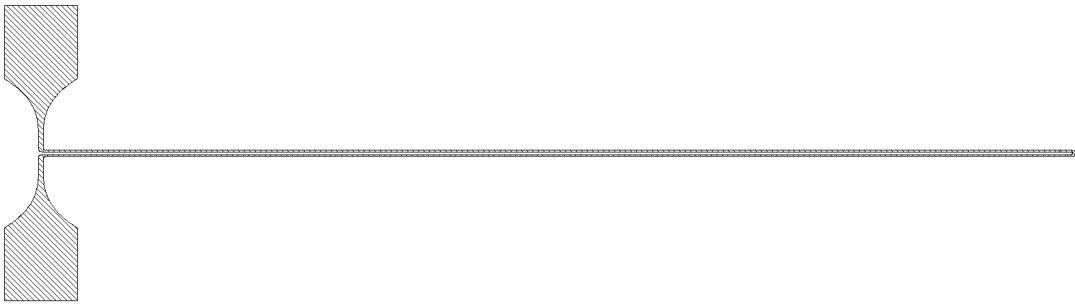

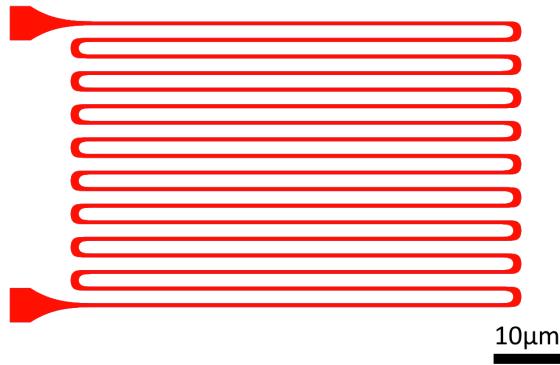

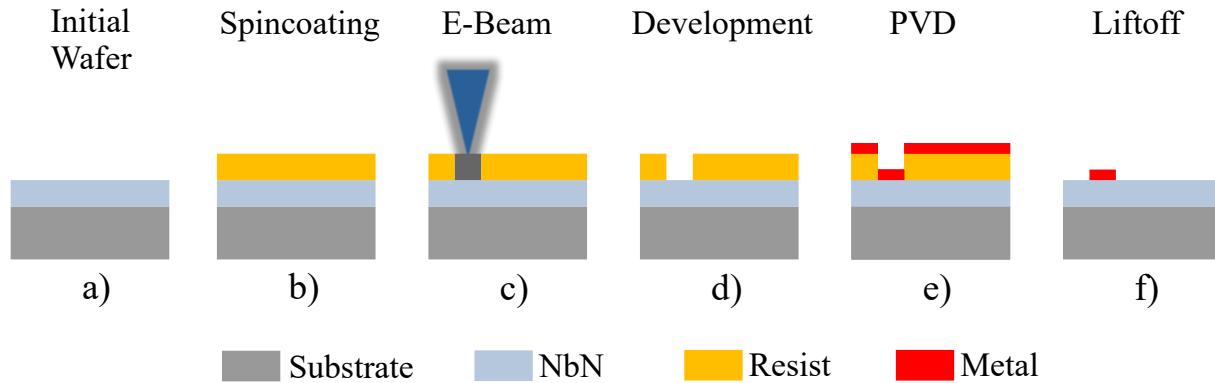

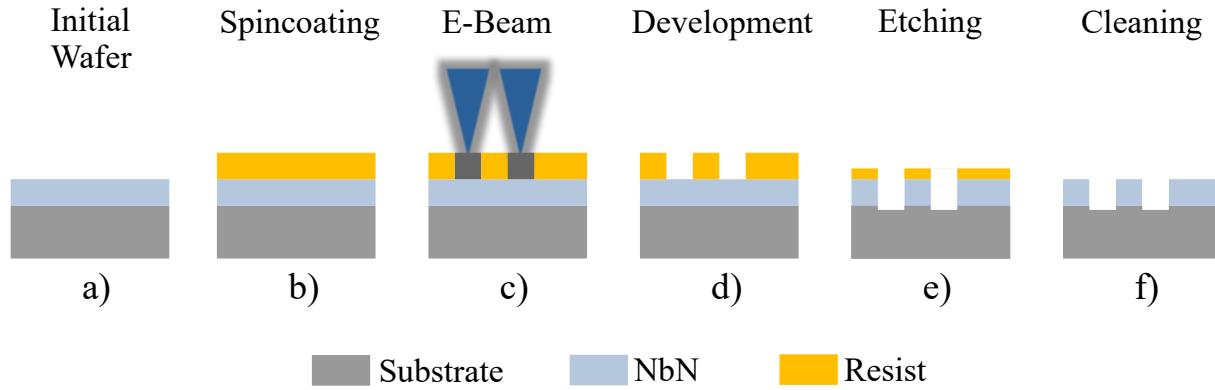

SNSPDs are thin nanowires, ca. 100nm wide and ca. 5nm thick, which are made out of some superconducting material. In the top-down fabrication approach, the superconducting material is first deposited as a thin film on a wafer and then etched after lithography [9]. For integrated photonics, SNSPDs are patterned in a U-shape on top of a waveguide material. An impression of such an SNSPD is given in figure ??, which displays the true relative sizes between width and length, as used for fabrication.

A typical superconducting material of choice is NbN [23][24], which has a relatively high critical temperature  $T_c$  of 8-10K and is polycrystalline. It proved to have good compatibility and yield with SiN, and due to it's faster thermal relaxation time it results in superior count rates compared to other materials such as NbTiN or amorphous silicides [25].

Silicides, such as WSi and MoSi, have the advantage of being amorphous, making them compatible with multiple platforms [26] [27]. They need to be operated however at lower temperatures, requiring sub-K cryogenic systems.

Figure 2.1: Design of an SNSPD at correct relative scale. The thin U-shaped part is sensible to photons, the large pads allow connection to electronic circuits.

Their amorphous structure results in slower thermal relaxation and thus reduced timing performances [28]. It has been observed that they can give a higher yield at large scales, which is why they can be a preferred material e.g. for large detector-arrays [16].

An SNSPD is operated as single-photo-detector by biasing it near to its critical current  $I_c$ , which is the maximum current the SNSPD can support without breaking the superconducting state. When a photon impinges on the SNSPD and is absorbed, a local resistive domain forms across the nanowire, giving rise to a measurable voltage signal.

### 2.1.2 Integration on-chip

Two distinct geometries have emerged for how SNSPDs are patterned on-chip: Bulk-SNSPDs and waveguide-integrated SNSPDs [29]. The geometry is intimately linked to how light is coupled to each respective detector type.

Bulk SNSPDs are created by patterning the nanowire in a long meandering shape, such that it completely fills a specific area on the chip, typically on the order of hundreds of square  $\mu\text{m}^2$  [30]. Light is coupled to such a bulk SNSPD via a lensed fiber that is placed vertically on top of the chip and collimates the light onto the meander area.

Waveguide-integrated SNSPDs are created by patterning the nanowire in a U-shape atop a photonic waveguide, with a typical length of 50-100  $\mu\text{m}$  depending on the waveguide material and figure of merit for the specific detector [9]. This allows the nanowire to have a high detection efficiency, as the light for detection is guided directly below it. Waveguide-integrated SNSPD can achieve near unit detection-efficiency even in the low photon energy IR regime, as for example for the 1550nm telecom wavelength [31] [32] [33]. The ability to interface with the waveguides allows photon creation, manipulation, and detection all on the same chip [34]. The reduced footprint compared to bulk allows higher integration densities.

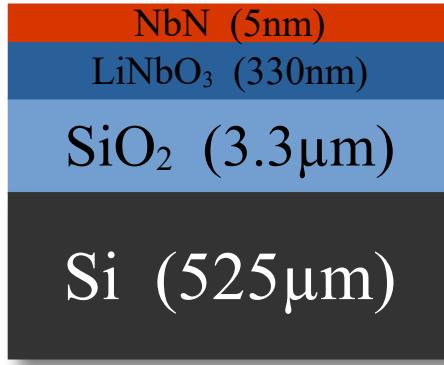

The material stackup of a photonic chip wafer is shown in figure 2.2. The upmost layer

is the thin film of superconducting NbN (5nm), from which the SNSPDs are patterned. The next layer is LiNbO<sub>3</sub> (330nm), from which the integrated waveguides and electro-optic modulators can be fabricated [35]. The SiO (3.3μm) provides adhesion for the LiNbO-layer as well as a refractive index contrast, such that light guided in the LiNbO-layer does not leak into the substrate below. The Si (525μm) provides mechanical stability for the whole chip, i.e. it prevents breaking and bending.

Figure 2.2: The wafer stack of a photonic chip. Waveguides and EOM are patterned into the 330nm LiNbO<sub>3</sub> layer, the SNSPDs into the 5nm NbN film. The SiO<sub>2</sub> provides refractive index contrast and the Si provides structural stability.

### 2.1.3 History

SNSPDs were introduced by Golt'smann et al. in 2001 [36], employing for the first time NbN nanowires for single-photon-detection, setting the basis for todays SNSPDs. Theoretical work in 2009 showed how such SNSPDs could be applied to integrated photonics [37], with first experimental realisations following by Sprengers et al. in 2011 [38] and Pernice et al. in 2012 [29].

Before the advent of SNSPDs, superconductivity was already exploited for photon detection via other techniques. One of the most popular methods was (and is) the Transition-Edge Sensor (TES) [39]. Research into Transition-Edge-Sensors already started in the 1940s [40] and was refined from there on for decades [41] till today [42]. It is this long research into superconductivity, photo-detection, cryogenics and readout techniques from which SNSPDs could emerge. TES are employed in many areas of research, for example as large detector arrays in astronomy [43]. Their sensitivity and operation principle gives direct ability for photon number resolution [44].

TES can also serve as an instructive comparison to appreciate how SNSPDs differ from their predecessors. TES are operated in the superconductivity transition range very close to  $T_c$ , while SNSPDs are operated well below  $T_c$ . In TES, an absorbed photon modifies the resistance of the detector by locally increasing the detectors temperature. To be this sensitive, TES need to be operated on temperatures on the order of 50mK and stabilized with mK-precision [45], to have fine control on the devices thermal capacitance.

In SNSPDs on the other hand, the detection mechanism is related in part to the electric current in the nanowire, relaxing the requirements on temperature control (in comparison). For SNSPDs, cryogenic setups in the range of 1-2 K are typically sufficient.

### 2.1.4 Detection mechanism

Different phenomenological models have been reported to describe the detection mechanism in SNSPDs: Hotspot-models and magnetic-vortex-models [25]. They are complementary: the hotspot-model applies especially to high energy photons and large bias currents, while the vortex-model gives better predictions for detection of low energy photons and low bias currents.

The hotspot-model was first proposed by Goltsman [36] and provided a sufficient prediction of most of the detector mechanisms [46]. However, further research showed that it contained distinctly wrong predictions for edge cases such as low-energy photons and dark counts. This led into research of magnetic-vortices [47] which proved successful in predicting experimental curves.

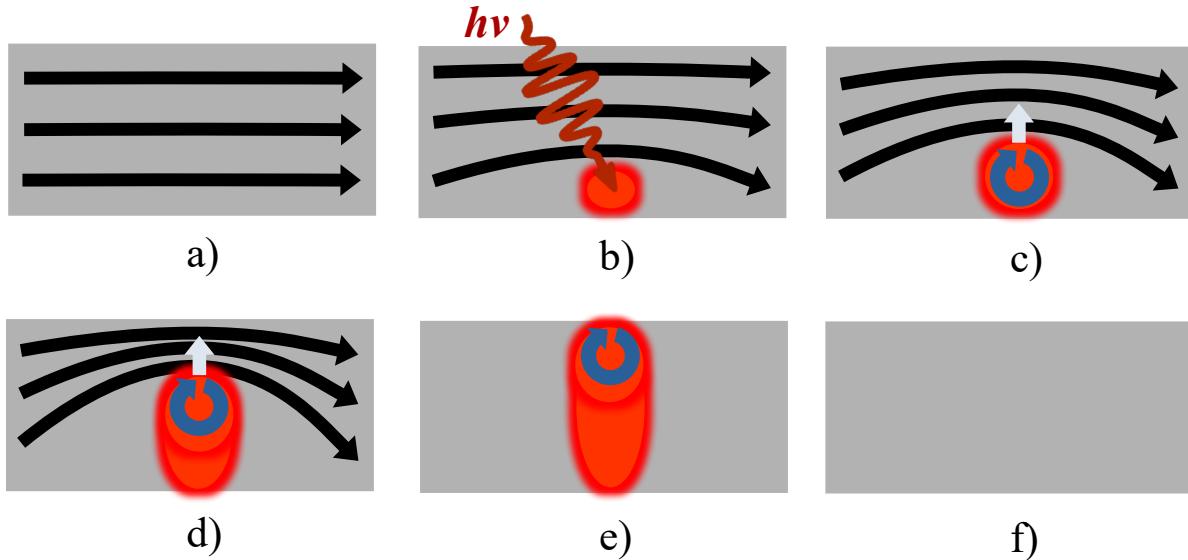

Figure 2.3: Vortex-Assisted Hotspot Model

A thorough discussion of such models and the underlying physics is given in [48]. Here, I sketch the detection mechanism following a vortex-assisted hotspot-model [47]:

1. **Photon absorption:** A photon is absorbed by the superconductor, e.g. via perpendicular illumination or evanescent coupling through a waveguide (b).

2. **Thermalisation:** The photon transfers its energy onto the paired electrons (Cooper Pairs), exciting them into a quasi particles (QP) state. These exited QP can collide with other Cooper-Pairs, exciting them into the QP state as well. A local excess

density of such QP is called a hotspot. QP can loose their energy also via interaction with surrounding phonons, in which case the energy is dissipated into the substrate and the QP thermalize.

3. **Vortex-Unpinning:** Within a hotspot, the excess of QP creates an area of locally suppressed superconducting order parameter. This lowers the energy barrier needed for a vortex crossing. A magnetic vortex is created and unpins from the sidewalls (c).

4. **Vortex-Crossing:** The magnetic vortex experiences a Lorentz Force due to the still flowing current. The Lorentz Force pushes the vortex perpendicular across the nanowire. Along the path of the Vortex superconductivity is further disturbed, expanding the hotspot (d).

5. **Formation of a resistive domain :** As the vortex travels across of the nanowire, the energy released by this crossing can suffice to destroy superconductivity in the area of the hotspot. A resistive domain across the nanowire is formed (e). Further current that flows through the nanowire heats the resistive domains due to joule heating  $I^2R$ . This heating effect can increase the local temperature by multiple degree Kelvin.

6. **Signal creation:** The sudden switch of a small section of the nanowire into a resistive state creates a voltage signal that propagates in both directions away from the resistive spot. This voltage signal can be detected with appropriate electronics. The precise extend of the resistive domain depends e.g. on the photon energy and the nanowires inductance (e).

7. **Reset:** The hot resistive domain cools down by dissipating it's energy via electron-phonon and phonon-phonon interactions into the substrate. After some reset time, the nanowire is ready for the next detection (f).

### 2.1.5 Fundamental properties

I introduce here four of the most fundamental properties of an SNSPD: It's normal state resistance, it's kinetic inductance, it's critical current and it's hysteresis current. These form the basis upon which I can discuss further dynamics.

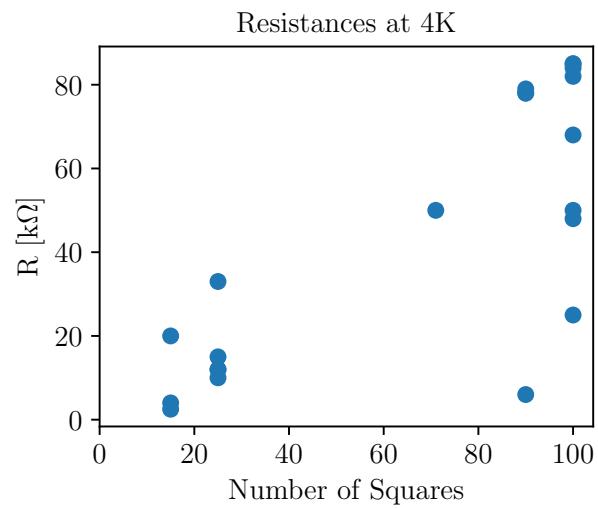

#### Normal state resistance

When a part of the nanowire is in it's resistive state, it still allows current to flow, but now against some resistance. This resistance is material-specific, for ca. 5nm thin NbN films for example it lies [25][49] in the range of

$$R_{sq} \approx 300 - 700 \Omega/\text{sq} \quad (2.1)$$

This is read as "Resistance per square" and means: If a wire is 1 $\mu\text{m}$  long and 100nm wide, it can be modeled as being made up out of 10 identical squares, which the current has to

pass sequentially. Each square presents the current a resistance of  $R_{sq}$ . If say the specific material has a resistance  $R_{sq} = 500 \Omega$ , the wire would have a total resistance of  $5 \text{ k}\Omega$ .

Measuring resistances in squares is useful because the unit is invariant under scaling: If a wire were  $2\mu\text{m}$  long and  $200\text{nm}$  wide, it would still consist of 10 squares and have the same total resistance as above. This is because resistance of any wire scales linearly with it's length and inversely with it's width, such that a square offers the same resistance independent of it's scale.

Since one needs some value to work with for estimations, for the rest of this thesis I will use  $R_{sq} = 500 \Omega$  as an average [25] resistance value for  $5\text{nm}$  thin NbN wires.

### Kinetic inductance

Each superconducting nanowire has a kinetic inductance  $L_{kin}$ , which does arise due to the presence and flow of Cooper-Pairs. These charged carriers have mass and show inertia under the influence of external voltages. The inductance for each square of nanowire is

$$L_{sq} = \frac{\hbar R_{sq}}{\pi \Delta_0} = \frac{\hbar R_{sq}}{1.76\pi k_B T_c} \quad (2.2)$$

where  $\Delta_0$  is the superconducting band gap of the nanowire and  $R_{sq}$  is it's normal state resistance. The band gap can be expressed in terms of the critical temperature  $T_c$  via  $\Delta_0 = 1.76k_B T_c$  by the BCS theory. With e.g.  $T_c = 10 \text{ K}$  and  $R_{sq}$  from above I get an inductance of  $L_{sq} = 69\text{pH/sq}$ . If a wire were to have 10 squares, this would result in a kinetic inductance  $L_{kin} = 690\text{pH}$ .

A different derivation of the kinetic inductance allows to see the influence of the geometry more directly. For a nanowire with length  $l$ , width  $w$  and height  $h$ , the kinetic inductance is [15]:

$$L_{kin} = \frac{m_e}{2ne^2} \frac{l}{w \cdot h} \quad (2.3)$$

where  $m_e$  is the electron mass,  $e$  the electron charge, and  $n$  the electron density. The factor two arises due to electrons flowing as Cooper pairs. It can be seen that the kinetic inductance scales in proportion with the length of the nanowire and inversely with it's height and width. This allows to design nanowires with specifically chosen inductances.

Very close inspection of theory and experiment show that the inductance also slightly varies (by up to 10 percent) with the amount of actual current flowing in the nanowire [45].

In our group, a slightly higher value of  $L_{sq} \approx 0.5\text{nH/sq}$  was experimentally found for our NbN films. I will use this higher value for further estimations in this thesis, as it's assumed to be closer to the actual films I work with.

The inductance  $L$  in an electrical circuit determines and limits how fast a flowing current can change its magnitude and direction. Mathematically this is expressed via  $dI/dt = U(t)/L$ . Most inductors in electronics get this inertia via a magnetic field created by a spiral wire geometry.

Such a spiral geometry however is almost impossible to mimic with a flat superconducting film. It is thus interesting to note that these flat superconducting wires still have a material-intrinsic inductance through their Cooper-Pairs, independent of any larger-scale geometry.

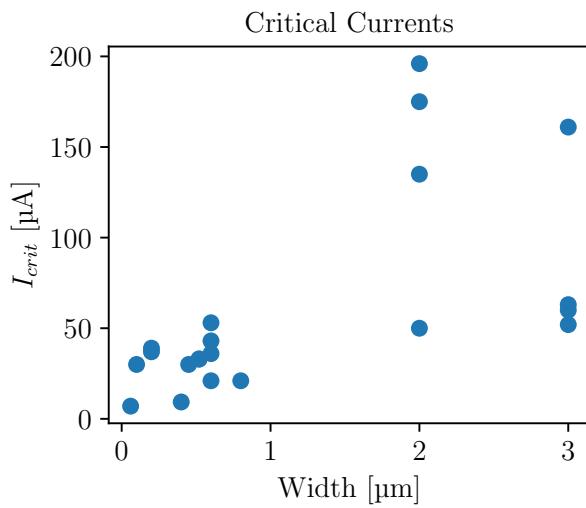

### Critical current

The critical current  $I_c$  of a nanowire is defined as the maximum current it can support in its superconducting state. Each superconducting material has some intrinsic critical current density  $j_c$ , which is the maximum current it can support per crosssection of wire. In a nanowire of width  $d$  and height  $d$  this relates the nanowires critical current and the materials critical current density via:

$$j_c = \frac{I_c}{wh} \quad (2.4)$$

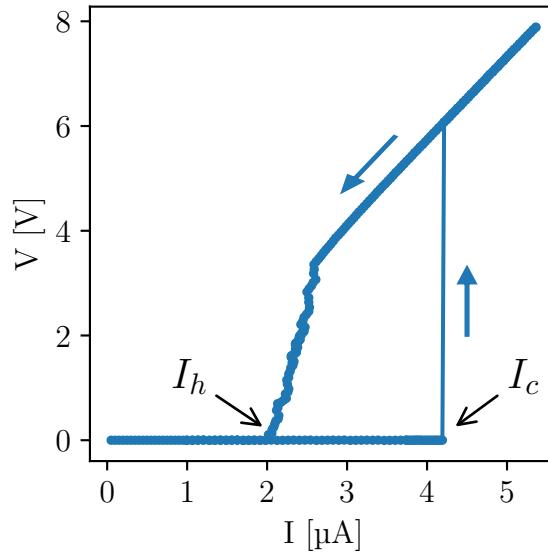

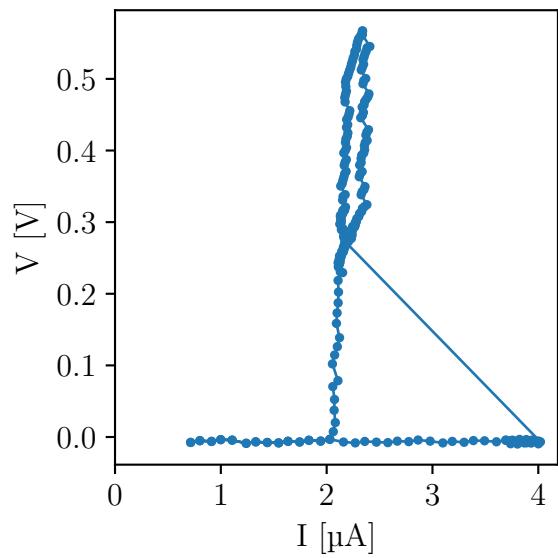

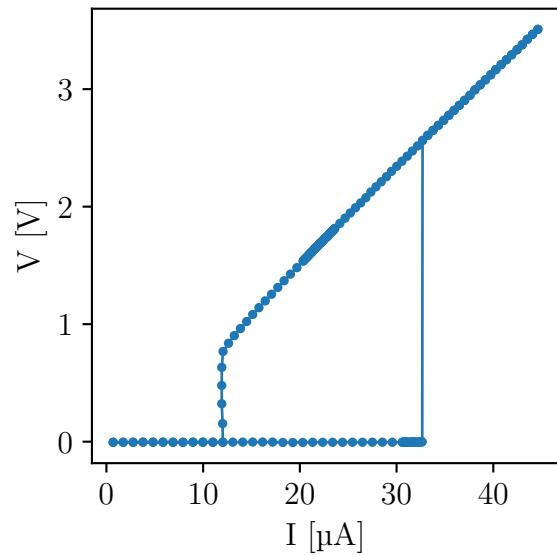

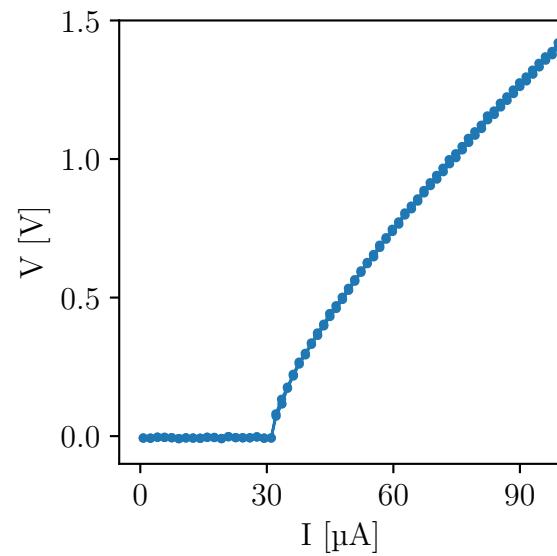

In figure 2.4 an IV-Curve of an SNSPD is displayed, in which the value of the critical current  $I_c$  can be seen by the sudden jump into resistivity. The biasing current was ramped up from zero to some maximum value and then ramped down again.

Figure 2.4: IV-Curve of an SNSPD, with annotated critical current  $I_c$  and hysteresis current  $I_h$ . The blue arrows indicate the progression of the scan.

The critical current density is temperature-dependant. The exact relationship  $j_c(T)$  can be calculated via the Ginzburg-Landau theory [50], given by the equation

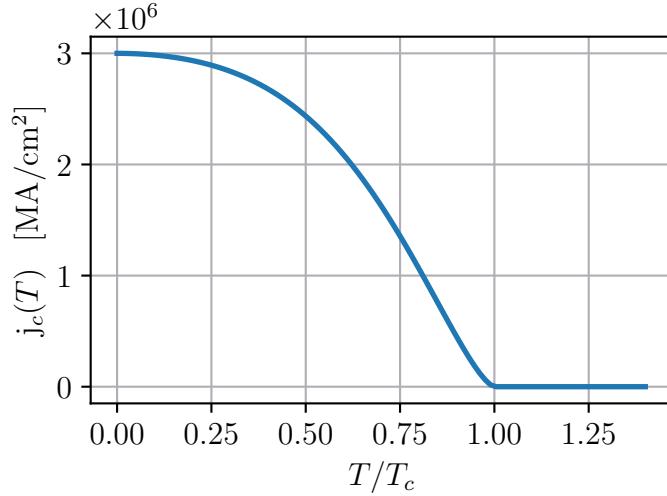

$$j_c(T) = j_c(0) \left[ 1 - \left( \frac{T}{T_c} \right)^2 \right]^{3/2} \left[ 1 + \left( \frac{T}{T_c} \right)^2 \right]^{1/2} \quad (2.5)$$

where  $j_c(0)$  is the critical current density at very low temperatures ( $T \ll T_c$ ). For NbN, this critical current density is ca.  $j_c(0) \approx 6 \text{ MA/cm}^2$  [51]. The exact value per material depends also on the quality of the deposited film.

Figure 2.5: The Ginzburg-Landau-Relation for the critical current density  $j_c(T)$

From the Ginzburg-Landau-Relation it can be inferred that for low enough temperatures (approx.  $T \leq 0.25T_c$ ) one can approximate the critical current density to a good degree as constant. For higher temperatures instead, the gradual decline in critical current density should be considered.

Experiments in our group showed that especially very thin nanowires don't exactly follow the relationship predicted by equation 2.4. Instead, there exists, among else, a small offset for very narrow wires. This is believed partly due to proximity effects to the substrate, as well as fabrication imperfections such as rough sidewalls. For low temperatures,  $T < 0.25T_c$ , our group [15] found the following fitted relationship for ca. 5nm thin NbN nanowires:

$$I_c(w) \approx -5 \text{ } \mu\text{A} + w \cdot \frac{10 \text{ } \mu\text{A}}{60 \text{ nm}} \quad (2.6)$$

which can also be inverted for the use the other way round, then reading

$$w(I_c) \approx \frac{60 \text{ nm}}{10 \text{ A}} \cdot (I_c + 5 \text{ A}) \quad (2.7)$$

For the remainder of this thesis I will use this experimental relationship as a reference when needed to relate critical currents to widths.

### Hysteresis current

The hysteresis current  $I_h$  marks the current at which the nanowire returns from the resistive back into the superconducting state, annotated in figure 2.4. The transition is due to

a electrothermal effect [52]: Once a nanowire switches to the resistive state, it's resistive domains are heated up via joule heating.

As long as a high current flows such that this heating is larger than the dissipation into the substrate, the nanowire stays at an elevated temperature and in a resistive state. This persists even if the current is reduced below the critical current  $I_c$ , giving rise to the hysteretic behaviour.

The hysteresis current  $I_h$  marks thus the threshold at which the joule heating drops sufficiently low such that the nanowire cools down, and returns to it's superconducting state. It can be analytically approximated as the current for which the following balance is fulfilled [53]:

$$\rho I_h^2 = 2h_c(T_c - T_s) \quad (2.8)$$

where  $\rho$  is the normal state resistance of the nanowire per unit length,  $h_c$  is the thermal boundary conductance between nanowire and substrate,  $T_c$  is the critical temperature of the nanowire and  $T_s$  the substrate temperature. The hysteresis current is thus dependent on the thermal environment surrounding the SNSPD.

This poses a hard requirement for any interfacing circuit to an SNSPD: The circuit must be designed such that at some point after photon detection the current through the nanowire falls below  $I_h$ , as otherwise the nanowire does not return to superconductivity.  $I_h$  in turn depends on static properties of the nanowire ( $\rho$  and  $T_c$ ) as well as on the thermal interface to the substrate ( $h_c$  and  $T_s$ ).

### 2.1.6 Circuit dynamics

We can now discuss the circuit dynamics after a photon absorption. The circuits dynamics arise because an SNSPD is embedded in an electrical circuit that delivers the necessary bias current and passes through the detection signal.

#### Equivalent electrical model

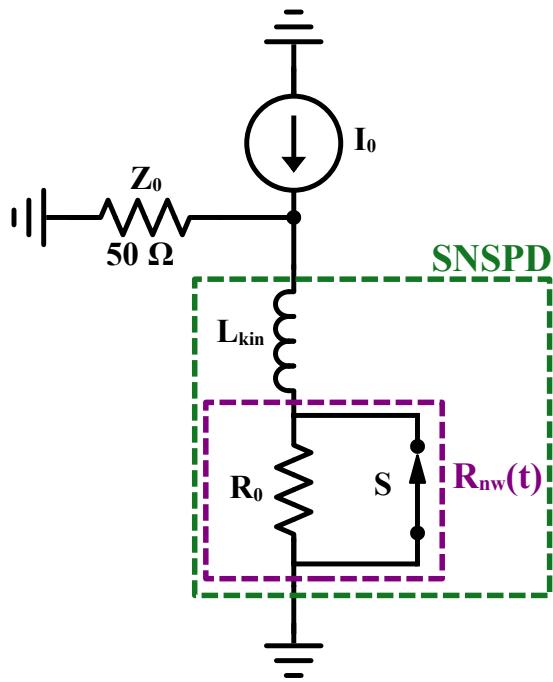

To help theoretical analysis and simulation, SNSPDs can be expressed via an equivalent electrical model. One of the first proposed models was by Kerman et al. [24], shown in figure 2.6. The kinetic inductance of the SNSPD is modelled via an fixed inductor and the transient appearance of a resistive domain via a fixed resistor and a switch. Changing the state of the switch in time allows to model the change between superconducting and resistive state of the nanowire.

#### Interfacing Circuit

Figure 2.6 not only shows the SNSPD, but also a basic interfacing circuit: A current source that delivers a constant bias current  $I_0$  to the SNSPD, and in parallel to the SNSPD a load impedance of  $50\Omega$ , modelling the typically  $50\Omega$ -matched impedance of any transmission line. This is a basic possible interfacing circuit and often employed [46][53].

Figure 2.6: Equivalent Electrical Model of an SNSPD plus surrounding interfacing circuit

Figure 2.7: LTspice simulation of an SNSPD-Click after photon absorption

### Photon detection cycle

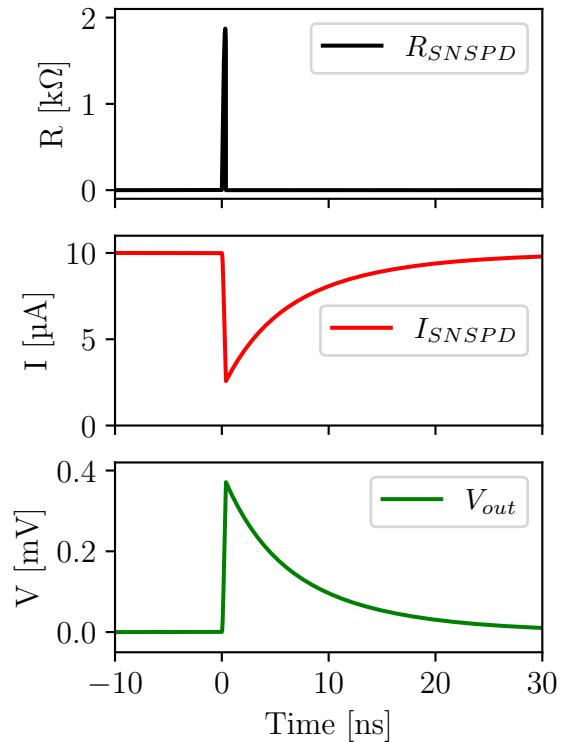

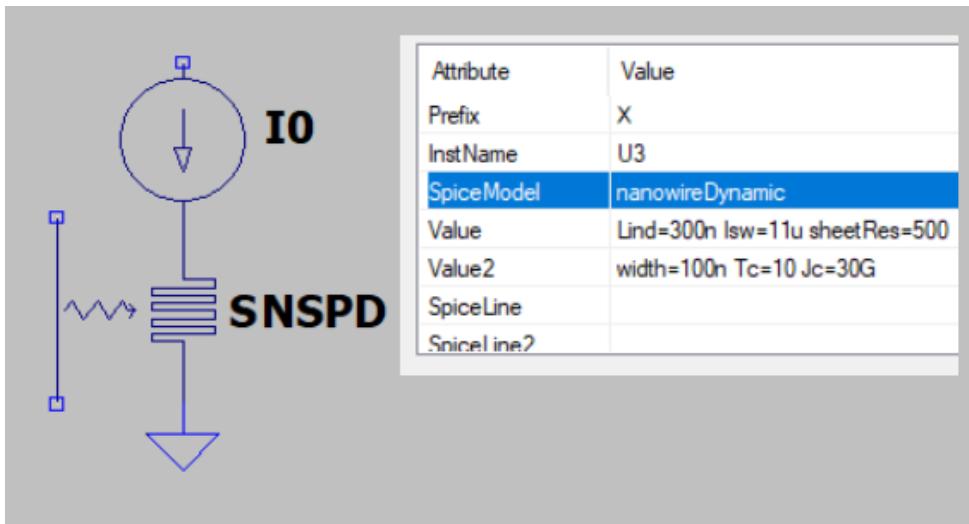

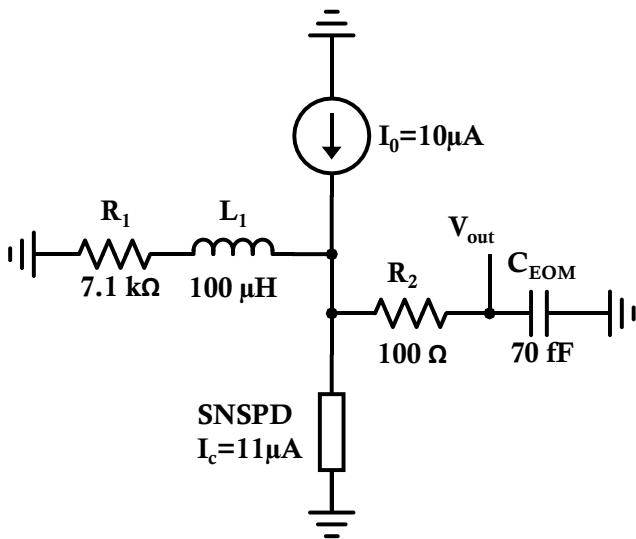

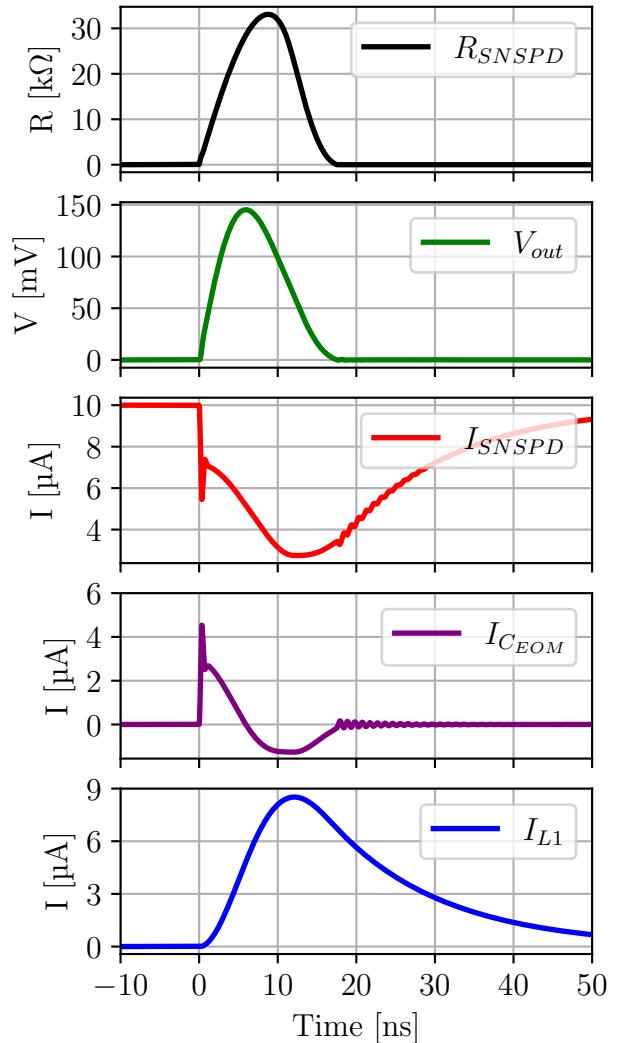

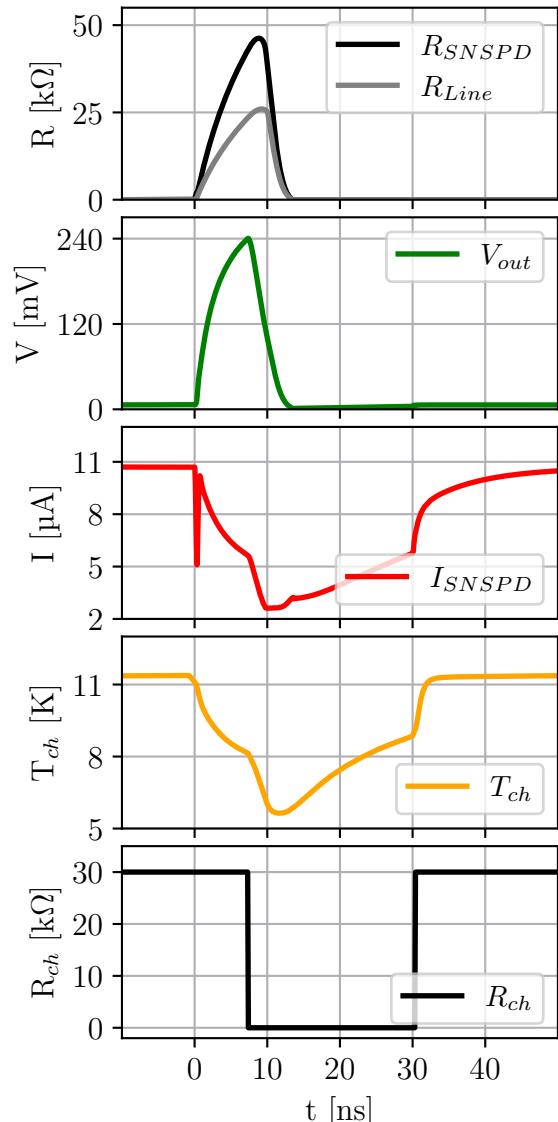

I now present a first view into the interplay between SNSPD and interfacing circuit after photon absorption. A simulation of the interfacing circuit is given in figure 2.6. To simulate SNSPDs, I use the SNSPD-Library developed by the group of Berggren [54] for LTspice. Further details on the software are given in section 4.1. The simulation results with a photon absorption at  $t=0$  are shown in figure 2.7, with which refer to to describe some main dynamics:

- **Resistive domain size:** After the photon absorption the SNSPD develops quickly a resistive domain, on the order of  $1-2\text{ k}\Omega$ .

- **Redistribution of current:** As soon as the resistive domain has formed, the biasing current redirects to a large part away from the SNSPD and into the load impedance  $Z_0$ , as it offers a much less resistive pathway to ground.

- **Superconducting reset** Once the current in the nanowire is reduced below it's hysteresis current  $I_h$ , it cools down and returns to it's superconducting state.

- **Output voltage:** A voltage signal of approx.  $V_{out} = I_0 \cdot Z_0$  is created over the load, with magnitude on the order of  $0.5\text{mV}$ . This is the signal that can be detected by further electronics.

- **Detection reset time:** The bias current does not immediately return into the nanowire, but only after some characteristic time delay given by  $\tau = L_{kin}/Z_0$ . The SNSPD is only sensitive to a next photon once its current is close to the original bias current, thus the delay  $\tau$  sets a limit to the count rate of the detector.

### 2.1.7 Latching

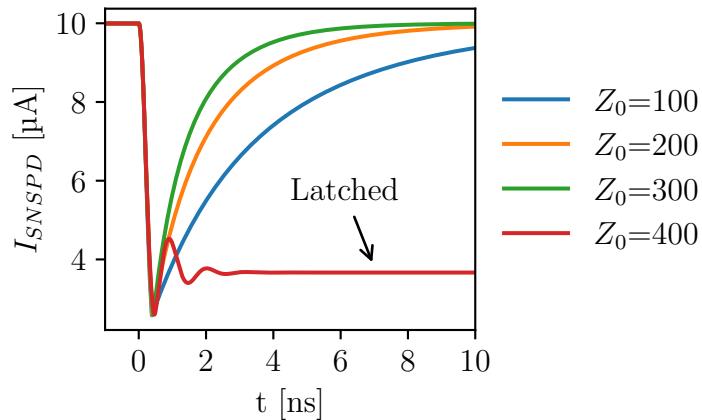

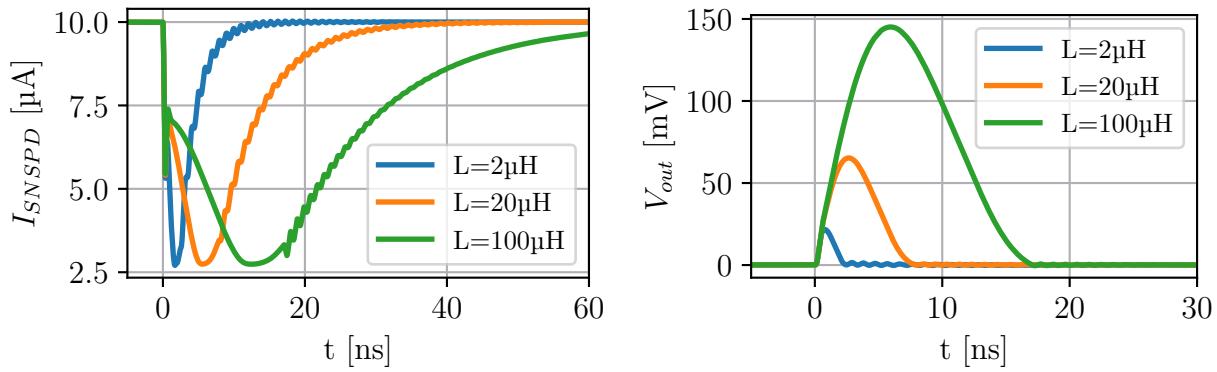

As the detection reset time of the SNSPD is given by the time constant  $\tau = L_{kin}/Z_0$ , a natural attempt would be to just increase  $Z_0$  to shorten this downtime. This approach is indeed possible, but only to some degree. In figure 2.8 an SNSPD click with four different readout loads  $Z_0$  ranging from 100 to 400  $\Omega$  is simulated, using the standard circuit from figure 4.1.

Figure 2.8: The resetting dynamics of a nanowire under different load impedances. The high load impedance of  $Z_0 = 400 \Omega$  leads to permanent latching, impeding any further photon detection.

For load impedances up to  $Z_0 = 300 \Omega$ , the detection reset time is indeed shortened. However, if the load is pushed further to around  $Z_0 = 400 \Omega$ , something qualitatively different happens: The circuit latches [52]. The current returned so quickly into the SNSPD that the resistive domains didn't have enough time to cool down, but instead are heated now persistently by joule heating. This traps the nanowire in a permanent resistive state, where it is not sensitive to any new photons.

When designing any new SNSPD readout circuit, it is thus absolutely necessary that the bias current at some point in time drops below the hysteresis current  $I_h$  of the SNSPD, such that it can reset back into its superconducting state [55].

A note: latching can also be influenced by other factors such as intense photon irradiation, which is encountered especially at high photon count-rates [56]. The photon irradiation can increase the bias current due to excess charges in the readout circuit, leading to latching behaviour that would be absent at lower photon counts. In scope of this

thesis however, I restrict my analysis of latching to electronic and thermal effects, i.e. in the limit of low photon counts.

### 2.1.8 Further details

I comment here on an adjacent topic about nanowires which do not fit directly in any of the above topics, but which is relevant.

#### Hotspot growth

The resistive hotspot in an SNSPD grow and relax dynamically [53], which can be described analytically. If a current  $I$  close to  $I_c$  flows through an SNSPD, and the SNSPD already has a resistive hotspot, then the spatial growth velocity of this hotspot can be approximated via [57] :

$$v_{HS} = \frac{2}{cw} \sqrt{\frac{\kappa R_{sq} I^2}{d(T_c - T_{sub})}} \quad (2.9)$$

where  $c$  is the specific heat of the nanowire,  $w$  is its width,  $\kappa$  its thermal conductivity,  $R_{sq}$  the normal state resistance,  $d$  the film thickness,  $T_c$  the critical temperature of nanowire and  $T_{sub}$  the substrate temperature. The factor two arises because the hotspot has two boundaries [57]. For NbN, the thermal parameters are  $c = 4400 \text{ J/m}^3\text{K}$  and  $\kappa = 0.108 \text{ W/(mK)}$ [57]. If one assumes a typical SNSPD with  $d = 5\text{nm}$ ,  $w = 100\text{nm}$ ,  $R_{sq} = 500\Omega/\text{sq}$ ,  $T_c = 10\text{K}$ ,  $T_{sub} = 2\text{K}$  and remaining bias current  $I = 6\mu\text{A}$  after an initial hotspot has formed, we get a hotspot growth velocity of

$$v_{HS} \approx 1.0 \text{ } \mu\text{m/ns} \quad (2.10)$$

That is, the resistive domain grows by one  $\mu\text{m}$  along the nanowire along every nanosecond. If the SNSPD is say  $100\text{nm}$  wide, then ten nanowire-squares turn resistive every nanosecond. With  $R_{sq} = 500 \Omega$  this leads to a change in resistance of  $dR/dt = 5\text{k}\Omega/\text{ns}$ .

Further details on hotspot dynamics can be found e.g. in the review by Gurevich [58]. One area where the growth speed of hotspot had to be explicitly taken into account was e.g. in fast superconducting microwave-switches [59].

## 2.2 Intermediate signal amplification

The typical voltage signal created by an SNSPD is on the order of  $1\text{mV}$ . This is too small to detect with typically available hardware such as oscilloscopes. Thus, the signal is almost always amplified by some means, into the regime of around  $100\text{mV}$  [17].

One popular method for such amplification are low-noise electronic amplifiers [60]. They are commercially available and can be inserted into the signal line right before the detection electronics. However, they also introduce noise in the signal, which can degrade detector performance [61].

In this section, I present three complementary techniques besides commercial amplifiers that allow to amplify signals of SNSPDs: Cascading, Impedance-Matching and On-Chip-Switches. All three methods exploit some specific property of SNSPDs (or superconductive elements in general). This can also give insight into the degrees of freedom that are possible in interfacing SNSPDs.

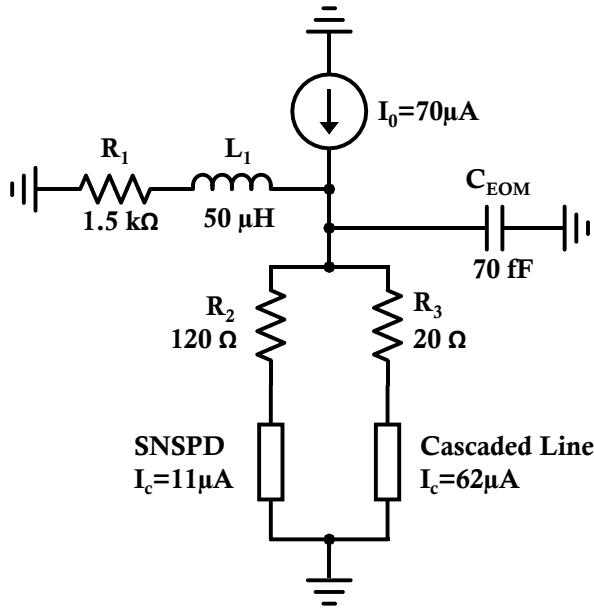

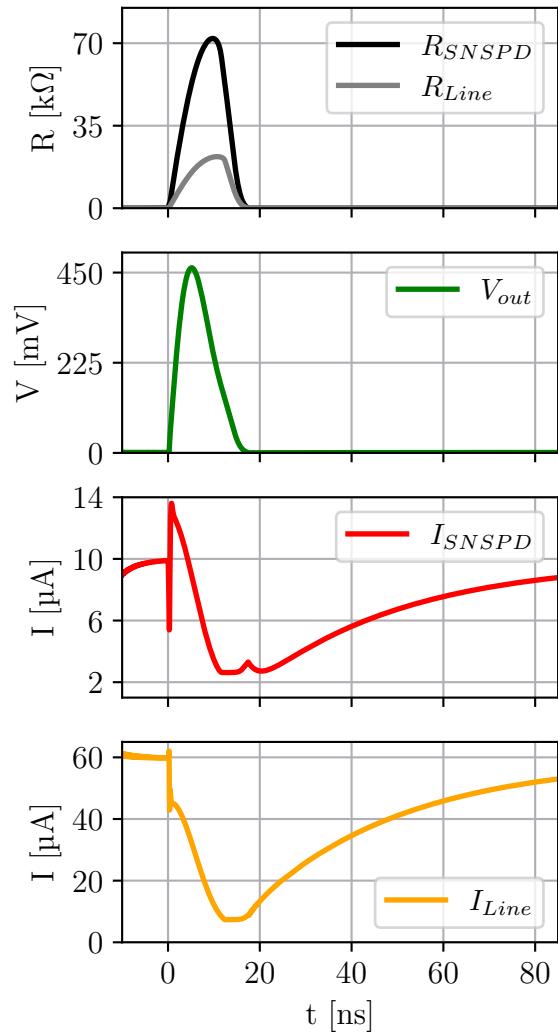

### Cascading

Cascading is a type of on-chip circuit design where an optically coupled SNSPD is connected to parallel superconducting wires with the aim of enhancing the response of the sensing element [62]. An exemplary circuit is sketched in figure 2.9 where three identical SNSPDs are added in parallel. The motivation behind this arrangement is the increase in total bias current  $I_b$ . The output voltage after a detection is approximately given by  $V_{out} = I_b \cdot Z_0$ , an increase in bias current (approximately) linearly increases the output voltage. Since a single SNSPD can only support current up to order  $10\mu\text{A}$ , parallel superconducting elements are needed to achieve higher overall bias current.

Figure 2.9: Cascading with 4 SNSPDs in parallel

To achieve a cascading effect, all elements must be initially biased just below their respective critical currents. When one SNSPD triggers due to a photon, its current gets redistributed to the other elements (still superconducting at that moment). If this redistributed current is then larger than the difference between bias current and critical current of the respective elements, they exceed their critical current as well and become also resistive. This leads ideally to a cascading effect until in short succession all involved elements are resistive.

A cascading of  $N = 5$  parallel elements was demonstrated in 2007 [62], called superconducting nanowire avalanche photon detectors (SNAP). Further works reported e.g.

$N = 12$  and  $N = 24$  elements [63] [64]. Such a design requires that all wires have the same critical current  $I_c$ , on which fabrication imperfections impose a limit. It was reported that already beyond  $N = 4$  parallel elements difficulties appeared regularly [65]. To relax such fabrication requirements, Binary Tree-Based cascading was proposed, where cascading happens in distinct hierarchies [65]. In some circumstances cascading can also be a harmful side effect that needs to be actively prevented [66].

### Impedance matching

Electrical Impedance extends the concept of resistance to alternating currents, and can describe frequency-dependent phenomena in electrical circuits (ref). The Impedance  $Z$  of a circuit element is given by

$$Z = R + jX \quad (2.11)$$

where  $R$  is the dissipative resistance to DC currents,  $j$  is the imaginary unit, and  $X$  is the reactance of the circuit element. The reactance is (in general) frequency-dependent. To note the most fundamental circuit elements: The impedance of Capacitors is  $Z_C = 1/jwC$ , the Impedance of inductors is  $Z_L = jwL$ , and the impedance of Resistors is  $Z_R = R$ . Transmission lines (such as coaxial cables) can be designed such that they present, from some lowest frequency point onwards, a constant frequency-independent impedance  $Z_0$ .

When two circuit elements with different impedances  $Z_1$  and  $Z_2$  are connected to each other, an incident wave to the interface is partly. The fraction of the reflected signal is given by

$$\Gamma_{12} = \frac{V^-}{V^+} = \frac{Z_2 - Z_1}{Z_2 + Z_1} \quad (2.12)$$

where  $V^+$  is the voltage of the incident wave and  $V^-$  that of the reflected wave. It can be seen that no reflection is only realised when the circuits have the same impedance. To prevent such reflections, most high-frequency electronics worldwide is standardized on a single impedance of  $Z_0 = 50 \Omega$ . For special cases, impedances of  $30 \Omega$  and  $70 \Omega$  can also be found.

For SNSPDs, numerical simulations show that during a detection event they have an impedance on the order of  $Z_S = 3 \text{ k}\Omega$  [67]. Interfacing such an SNSPD with a coaxial cable results in high reflection losses, diminishing any voltage signal from a detection event and limiting the transmitted voltage to approximately  $V_{out} = I_b \cdot 50\Omega$ .

A device that can interface between different impedances is an electrical taper [68]. It is, in essence, a conductive wire that is wide at one end and narrow at the other end, with a smooth transition of its width in between. One popular design choice is the Klopfenstein-Taper [69].

At the narrow end the taper has a high impedance  $Z_H$  and at the wide end it has some lower impedance  $Z_L$ , which both are determined (predominantly) just by this very geometry. The transition in the width has to be stretched out over a long enough length such that the electrical signals don't notice the gradual change in impedance [70].

By using such an impedance taper between SNSPD and coaxial cable, the voltage

amplitude of the signal can be increased by the factor [71]

$$G = \sqrt{\frac{Z_H}{Z_L}} \quad (2.13)$$

which would result for an SNSPD in a voltage signal increased by a factor  $\sim 8$ .

In regards of integrated photonics, one disadvantage of such tapers is their large footprint, which was reported up to 5mm x 3mm to interface a single SNSPD [72]. When a high density of detectors is desired, this prevents interfacing each single one with its own taper.

### Voltages response of lumped elements

Knowledge about the properties of circuit-elements can help in the design of circuits, as we have just seen in the example of the Impedance-Matching. Here I want to expand on this and give a minimal intuition into how voltages within a circuit form. For the three basic circuit elements Resistor  $R$ , Capacitor  $C$  and Inductor  $L$ , the voltage  $V_i$  that falls off over these elements is given by [73]:

$$V_R(t) = I(t)R \quad (2.14)$$

$$V_C(t) = \frac{Q(t)}{C} \quad (2.15)$$

$$V_L(t) = L \frac{dI(t)}{dt} \quad (2.16)$$

For a resistor, the voltage is given by the instantaneous current  $I(t)$  flowing through it. For a Capacitor, the voltage is given by the total charge  $Q(t)$  that has accumulated at it up to that point. For an Inductor, the voltage is given by the instantaneous *change* in current  $dI(t)/dt$  flowing through it.

Each of these elements develops its voltage over a different mechanism, and with different time scales involved. This knowledge might help to design circuits where the voltage of a specific element is maximized at some point in time. Which would be, for the outside observer, nothing else but also a signal amplification.

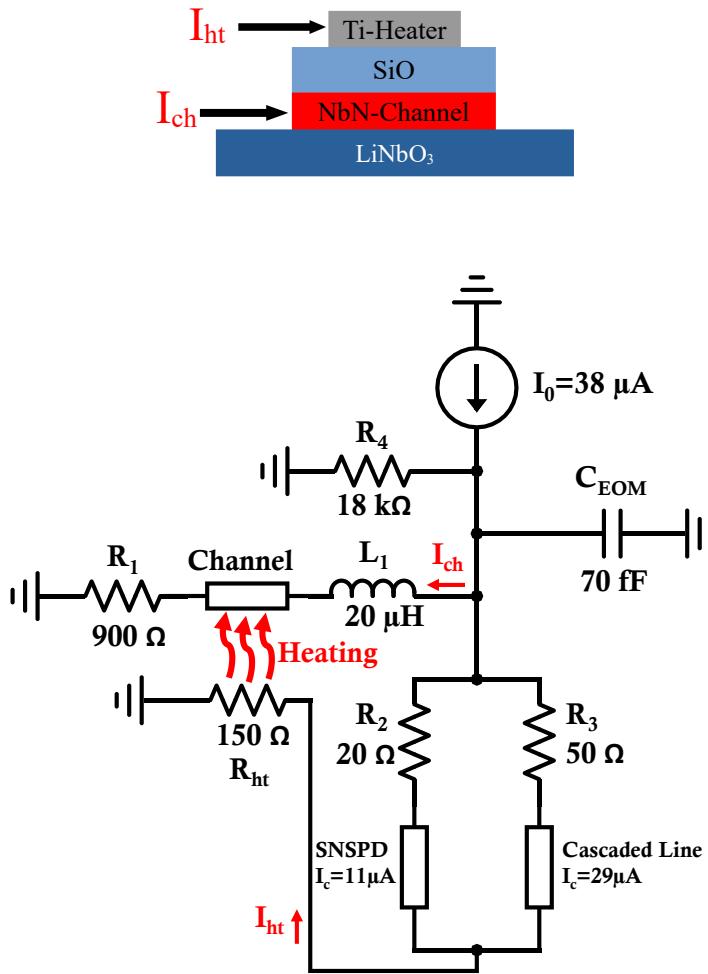

### Thermal switches

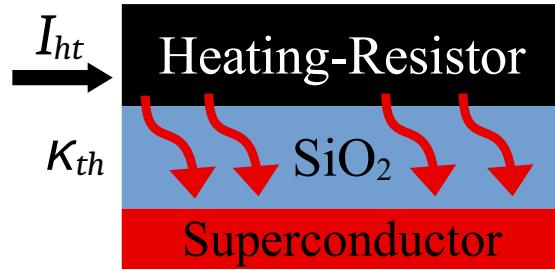

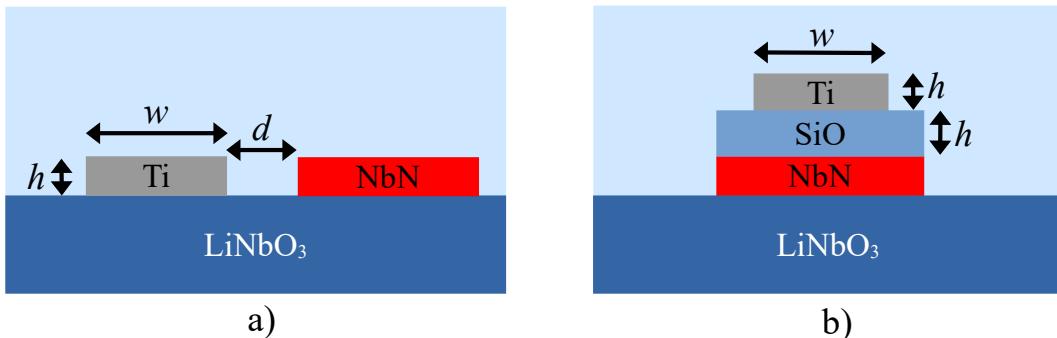

Heat applied next to a superconductor can directly destroy its superconductivity if the temperature reached is beyond the critical temperature  $T_c$  of the superconductor. According to McCaughan [74], such a heater idea was first demonstrated experimentally in 2003, coined a "Hot-Phonon-Switch" [75]. Figure 2.10 gives a sketch of such a heater setup.

Designs of with the heating element next to the superconductor [76][77] as well as the heating element on top of the superconductor [78] have been shown, with comments mentioning the need for the layered approach due to slow heat transfer in the planar design [78].

Figure 2.10: Sketch of a 3-layer thermal switch

A thin buffer layer is required between the heating element and the superconductor for layered switches, to isolate electrically. Employed materials for such a layer have been 10nm SiO [75], 25nm SiO [21] [79], 12nm  $\alpha$ Si [80], and 190nm SiO [81]. The last higher value was chosen specifically to reduce electrical capacitive crosstalk.

Thermal switches have the interesting property that the controlling current in the heating unit is electronically isolated from the controlled bias current in the nearby superconductor [80]. This allows for flexible circuit design and new coupling techniques [82] [21].

One application making use of this electrical isolation is the coupling between circuits with vastly different impedances. A vertically stacked 3-Layer-Switch allowed to transfer a signal thermally from a low-impedance circuit ( $50\ \Omega$ ) to a high-impedance circuit ( $400\text{k}\Omega$ ), resulting in a controllable voltage of 1.12 V in the second circuit [78]. This did not require any impedance matching, as electrical contact was completely bypassed. However, the response time can be increased, as thermal coupling is considerably slower than any electrical coupling.

Apart from photons, large electrical currents and heat, superconductivity can also be disturbed via a bit more exotic approaches. I want to mention here three in passing. Capacitor-coupled high-frequency gating signals that periodically drive the bias current beyond the critical current [59], creation of ballistic phonons via excess voltages of 4V and more [83] [84], and injecting non-equilibrium quasiparticles from one superconductor to a second nearby superconductor via tunneling effects [85] [86].

## 2.3 Readout of SNSPDs

In this last section I present the approaches employed in transmitting signals from cryogenics chips to the outside world, the last step of a signal registration. A main bottleneck in many schemes is the thermal load introduced by any sort of interfacing, limiting the readout capabilities of many devices in parallel [17].

I introduce first some basis of electronic readout, then a techniques that allow to address multiple detectors via a limited amount of wires, and present in the end optical

readout as qualitative different scheme for interfacing cryogenic chips.

### 2.3.1 Electronic readout

Since SNSPDs create a voltage signal, the most straightforward approach to carry this signal out of the cryostat is via some continuous electrical wiring. This is indeed the default approach taken in virtually every setup, it is robust and easy to implement.

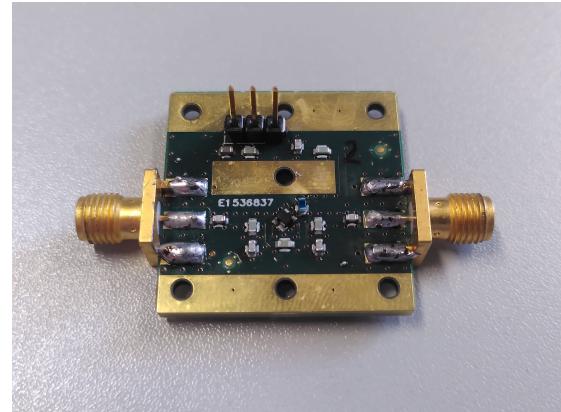

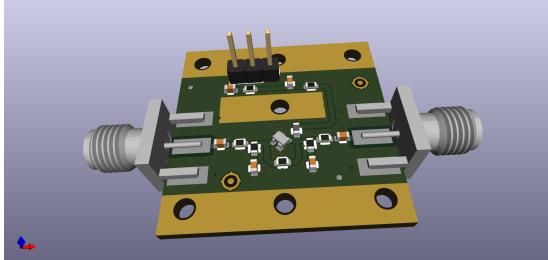

A general pathway for electronic readout is similar to the following [87]: The signal from the SNSPD (or any cryogenic device) first travels within the chip until it reaches a bondpad. Wirebonds transport the signal to a nearby surrounding printed circuit board (PCB) installed in the cryostat. Coaxial cables connect from there to the walls of the cryostat, where feed-through connectors pass the signal to the of the cryostat. There, low-noise amplifiers are often employed to increase the voltage signal from ca. 1mV to around 100mV [17], a voltage level which can then be registered with readout-electronics such as oscilloscopes, and digitized.

Due to the fact that each coaxial cable in such a setup is both in contact with room-temperature ( $\sim 300\text{K}$ ) and with the cryogenic stage ( $\sim 1\text{K}$ ), the number of coaxial cables is restricted by the cooling powers of the cryogenic system. As an estimate, each coaxial cables transports ca. 1 mW of heat into the cryogenic system [88]. Small cryostats can handle on the order of 10 mW and larger cryostats on the order of 100 mW heat input, but in any case, this limits the amount of coaxial cables to the order of 100.

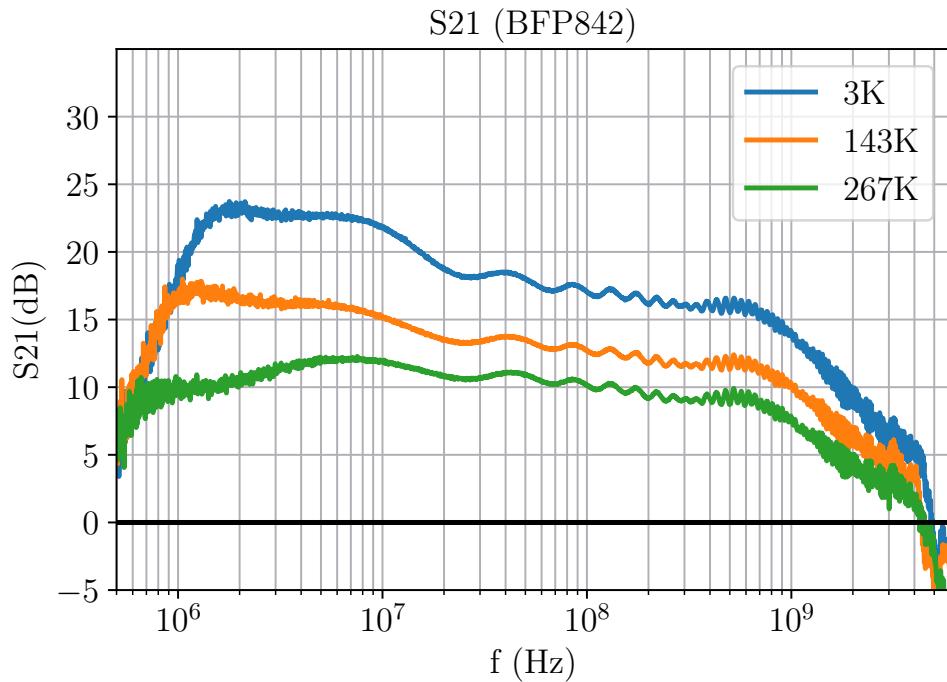

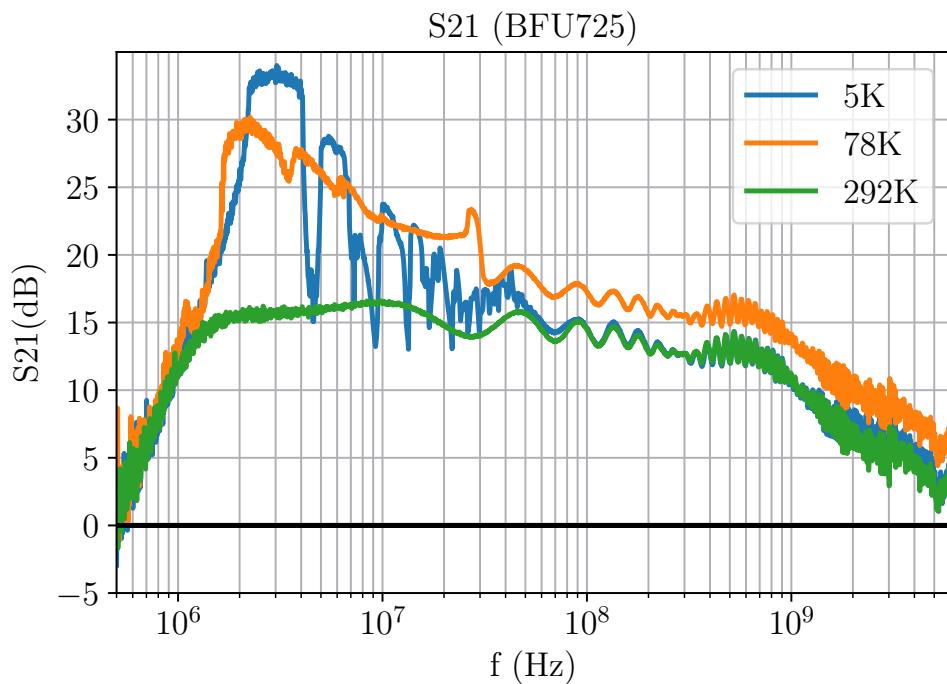

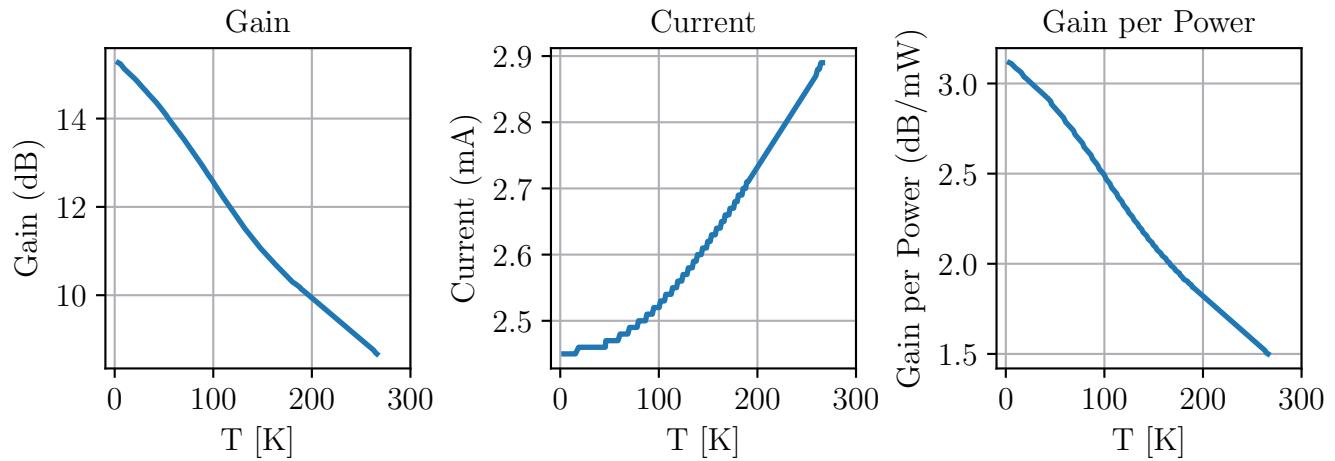

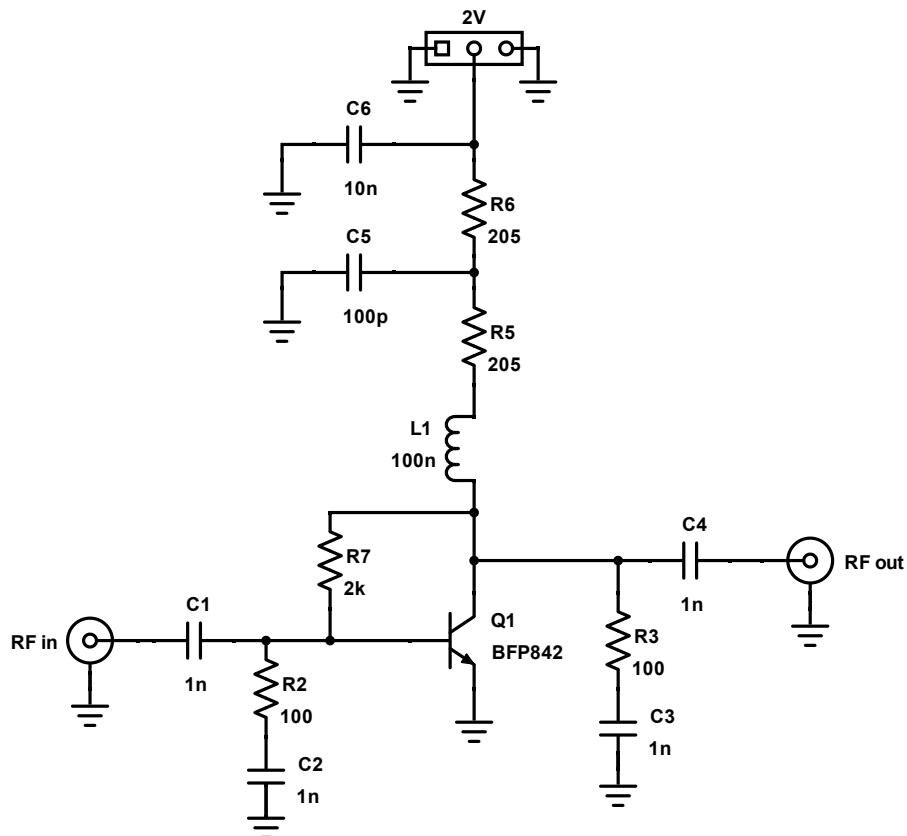

A similar argument concerns cryogenic amplifiers. One can install electronic amplifiers inside the cryostat to amplify the signal closer to the source. This has benefits such as reducing the Johnson-Nyquist noise, i.e. thermal noise [60]. However, even low-power amplifiers dissipate power on the order of 5-10 mW, limiting their number to only a few [61] [89].

To give an order of magnitude, the attenuation in cryogenic cables is ca. 3dB/m for frequencies in the range of 1-10 GHz [90] [91] [92]. The 3dB-attenuation marks the point at which a signals amplitude is reduced to half it's initial value. Since also noise increases with signal frequency, a typical bandwidth that is used to interact with SNSPDs is on the order of 1 GHz.

### Large-scale pixel-array readout

There is an ongoing effort in increasing the number of detectors per chip, because at some point, when scaling reaches into the thousands of detectors, this would allow to turn the chip into a camera. I present this topic also because it allows to observe trade-offs and limits of electronic readout particularly well.

Specific areas of interest for SNSPD-based cameras are in the deep-UV for astronomical applications [21] as well as the IR for biomedical imaging [93]. In such arrays, detectors are also referred to as pixels, which I adapt for this section.

To read out a large number of pixels (100-100k) with only few available coaxial cables (10-100) requires techniques to multiplex the detector signals, such that for each signal travelling through a coaxial cable the pixel of origin can be inferred [17]. I give a short summary of the development of such techniques, a condensed list is in table 2.1.

Table 2.1: Development of large-scale SNSPD readout techniques

| Year | Technique                | Scaling | Pixels (NxN)      | Readout Wires | Ref. |

|------|--------------------------|---------|-------------------|---------------|------|

| 2007 | Direct readout per pixel | $N^2$   | 2 (2x1)           | 2             | [94] |

| 2013 | Direct readout per pixel | $N^2$   | 12 (3x4)          | 12            | [95] |

| 2014 | Direct readout per pixel | $N^2$   | 64 (8x8)          | 64            | [96] |

| 2014 | Electric c.+ Time-tagged | $2N$    | 4 (2x2)           | 4             | [97] |

| 2017 | Time of flight (TOF)     | const.  | 590 (1)*          | 2             | [98] |

| 2019 | Electric c.+ Time-tagged | $2N$    | 1024 (32x32)      | 32            | [99] |

| 2020 | Thermal c.+ Time-tagged  | $2N$    | 16 (4x4)          | 8             | [82] |

| 2022 | Thermal c.+ TOF          | const.  | 1024 (32x32)      | 8             | [21] |

| 2023 | Thermal c.+ TOF          | const.  | 400,000 (500x800) | 8             | [16] |

\*590 effective pixels within a single long detector

Early work on large-scale pixel arrays started with direct readout of two pixels, which led to a maximum count of 64 pixels [94][96]. Further scaling was prohibitive, as for NxN pixels,  $N^2$  wires were required.

The number of wires could be qualitatively reduced with the introduction of electrical rows-column coupling, which together with a time-tagger allowed to read out NxN pixels with only  $2N$  wires, leading to up to 1024 addressable pixels [97][99].

Thermal instead of electrical row-column coupling was subsequently developed, which greatly reduced electrical cross-talk in large arrays [82]. By extracting spatial position via Time-of-flight measurements (as opposed to time-tagging), the number of required wires could be reduced further to a constant value (of 8 wires), independent of pixel count [98][21]. Via this combination of multiplexing techniques, all major theoretical roadblocks regarding scaling were eliminated.

The at present largest reported detector-array consists out of 400.000 pixels, all addressable via 8 wires [16]. The maximum count rate was up to ca. 100kHz, meaning that each single pixel could be read out on average once every 4 seconds.

### 2.3.2 Optical readout

Since electronic readout can be scaled up to large arrays only at the cost of reduced readout speed per detector (as seen in the previous section), new approaches for readout are being explored. One promising candidate is optical readout, based on interfacing the cryogenic chip through optical fibers via an external laser light [18]. Research in this area is motivated by the lower thermal load and higher bandwidth that optical interconnects can potentially offer [22].

I introduce the electro-optic-modulator, the core device that provides the link between electric and optic domain, and the present some recent developments within the field of optical readout.

### Electro-optical resonators

An electro-optic modulator (EOM) is a device that allows to modulate passing light via applying a voltage to the modulator. It is based on the electro-optic effect, also called pockels-effect [100], which is the change of optical properties of a material in response to an external electric field.

By applying a voltage to an EOM, the refractive index of the electro-optic material is changed slightly. Light passing through experiences this change in refractive index, which shifts it's phase. This phaseshift can then be exploited in various arangements to control the amplitude and direction of the light.

A popular electro-optic material is  $\text{LiNbO}_3$ , which has an electro-optic coefficient of ca.  $27\text{pm/V}$  [101]. Under the influence of an electric field, the polarized charges in it's crystal lattice rearrange spatially (slightly), changing the refractive index of the material.

In integrated photonics, the electro-optic effect of  $\text{LiNbO}_3$  can be exploited e.g. via Racetrack-Resonators [19]. These are closed-loop oval-shaped waveguides surrounded by electrodes. When a voltage is applied, the change in refractive index shifts the optical resonance frequency of the resonator. When light of a specific frequency is guided close to such a resonator, the resonator can be tuned to either absorb the light (if in resonance) or ignore it (if out of resonance). This allows to control the amplitude of the bypassing light via the applied voltage. For  $\text{LiNbO}_3$ -Racetrack-Resonators, reported modulation efficiencies have been for example  $3.2\text{pm/V}$  [102] and  $8.5\text{pm/V}$  [103].

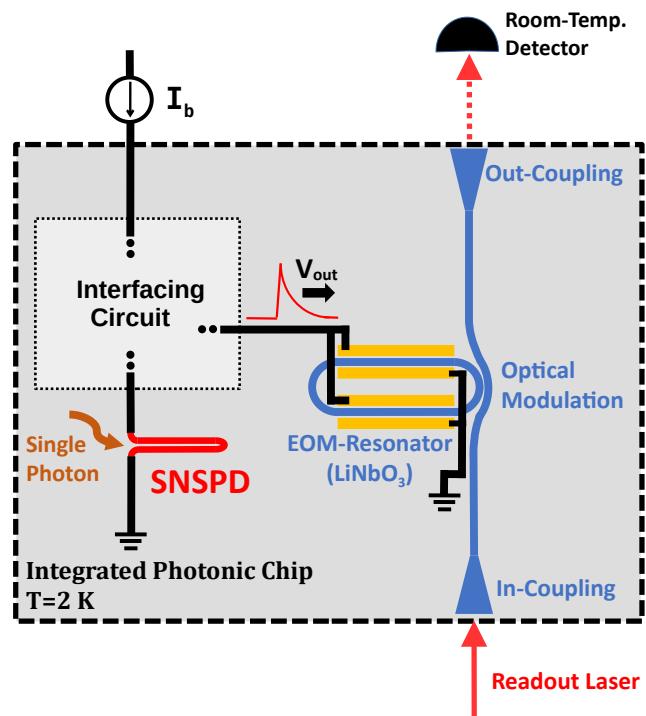

### Recent developments in optical readout

A general setup for optical readout follows these steps [22]: First, an external laser is coupled from room-temperature near to the chip via optical fibers, and is then coupled onto the chip via optical grating couplers. Integrated waveguides then guide the light within the chip where it is modulated by an integrated EOM. The EOM is controlled by the on-chip electric signals of interest, imprinting their signal onto the light. Finally, the now modulated light is coupled back out of the chip and guided again via fibers to some external detector at room temperature. By measuring the modulation, information originating from the chip can be retrieved.

This interface allows to transmit signals without any physical wires contacting to the chip. The laser light itself (and potentially any modulators on chip) do bring some thermal load as well, but compared to coaxial wires it is ca. two orders of magnitude lower [18]. Furthermore, strategies such as wavelength division multiplexing could be employed that would increase the bandwidth and allow to address multiple detectors on-chip at the same time. An example of a "photonic link" was recently reported in [104] with optical data

transfer rates in the GHz-regime.

A demonstration of optical readout specifically of SNSPDs was presented by de Cea et al. in 2020 [22]. A CMOS-integrated photonic ring-modulator was employed for the modulation, which provided a resonance shift of ca. 700pm/V. A device with such a high shift value was necessary because the SNSPDs provided only an output voltage of ca. 2mV. In combination, a resonance shift in the ring-resonator of ca. 1.4pm could be achieved after an SNSPD click, reducing the amplitude of a transmitted external laser temporarily by ca. 1%. This change in amplitude was then resolved by external photo detectors.

The setup was limited to the detection of UV Photons because only for those high-energy photons the detectors could generate a strong enough voltage signal. Additionally, the detector-design led to rather slow reset times on the order of 1 $\mu$ s.

### Sketch of the proposed setup within this thesis

At the end of this chapter a visual sketch of the proposed optical readout scheme is given, as motivated and introduced earlier (section 1.2). The sketch is given in figure 2.11. An SNSPD would be connected via a yet-to-be determined interfacing circuit to a LiNbO<sub>3</sub>-Racetrack-Resonator EOM, fabricated next to an integrated waveguide. When the SNSPD absorbs a photon, the voltage signal is transmitted (and ideally, amplified) via the interfacing circuit to the EOM. The voltage shifts the optical resonance frequency of the EOM, changing the strength with which the readout laser is coupled into the resonator ring. The resulting change in the laser light amplitude can then be registered by an external detector outside the cryostat.

Figure 2.11: High-Level sketch of the optical readout scheme which I work towards in this thesis.

# Chapter 3

## Simulating a cryogenic thermal switch

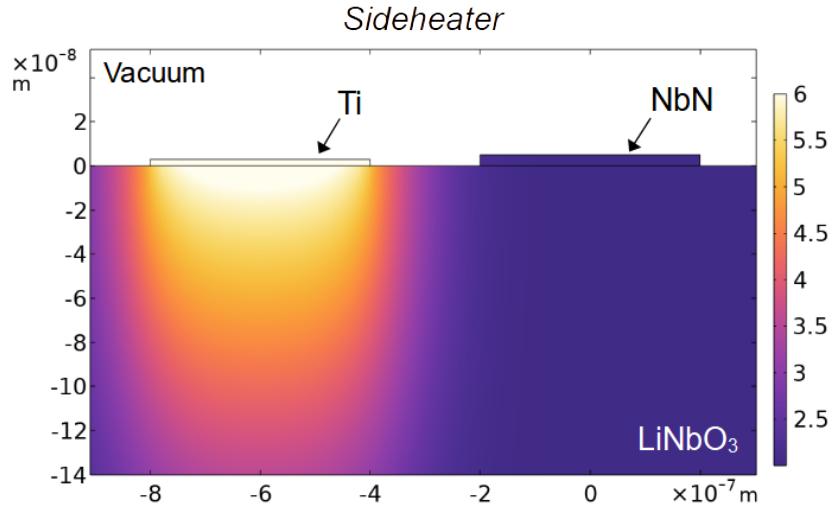

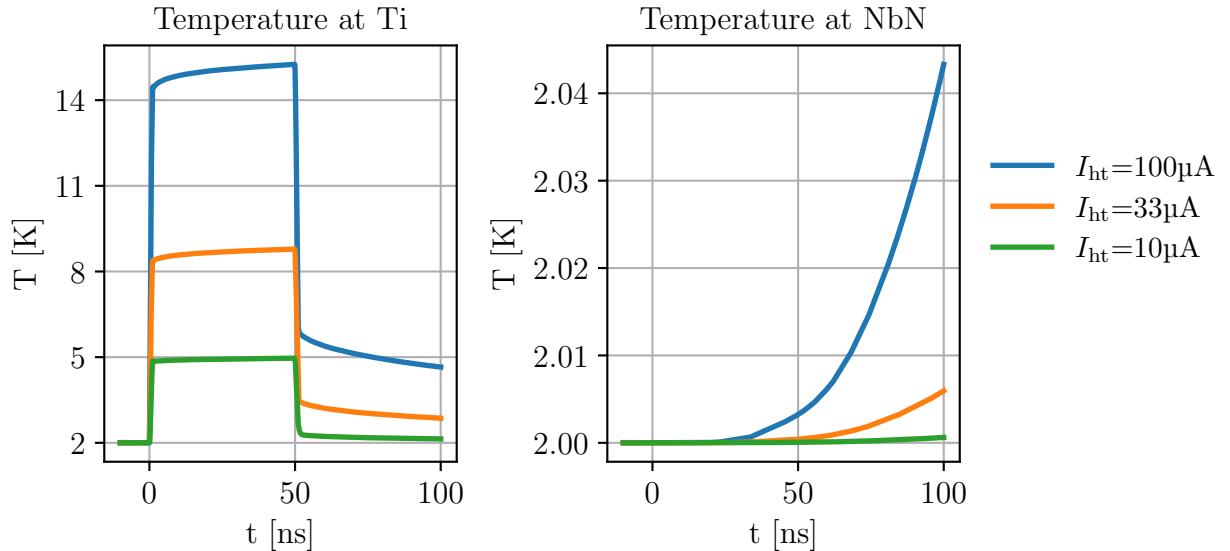

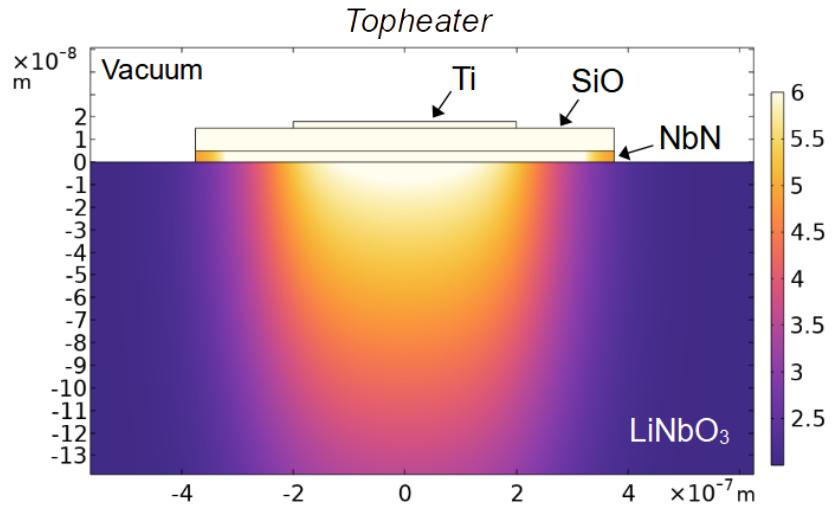

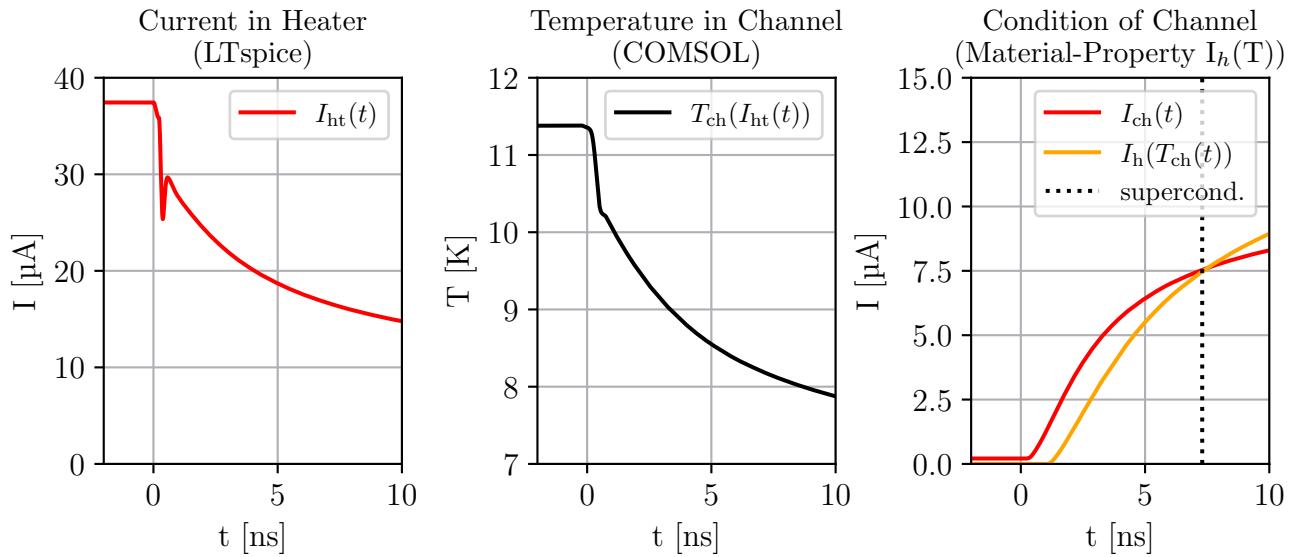

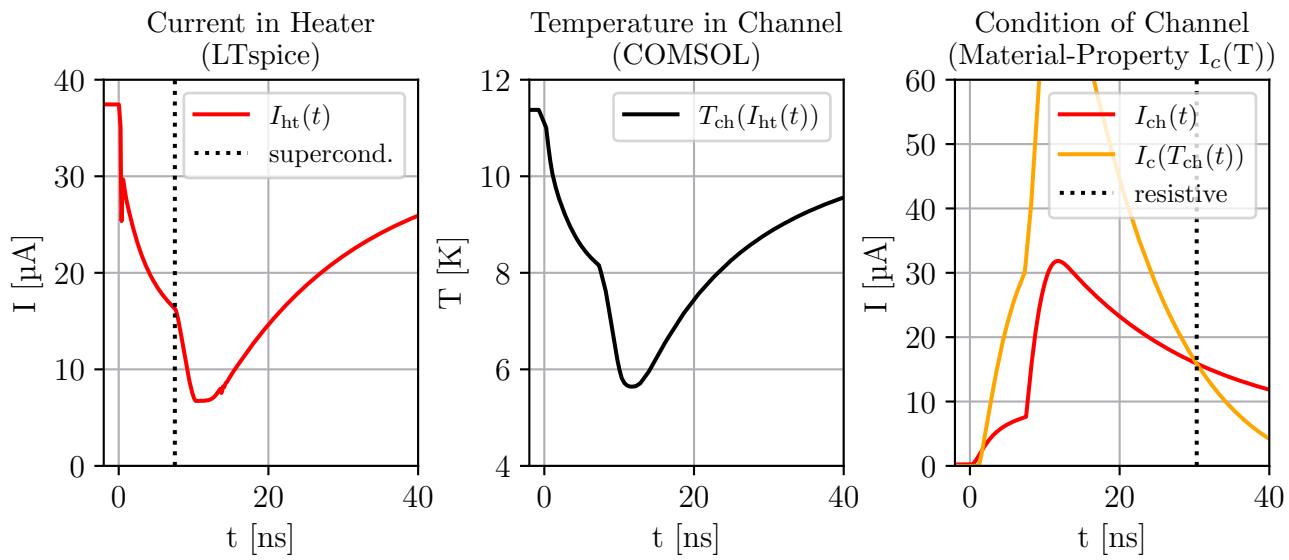

In this chapter I simulate the transient heat distribution of a cryogenic thermal switch, as presented earlier [2.2](#). The Motivation stems from the potential application of such a switch to the interfacing circuit between SNSPD and EOM, where it could provide during the detection cycle a controllable resistance and thus a re-configurable circuit.

Previous work about thermal switches (background [2.2](#)) showed that they were applied in similar cryogenic environments to ours, further motivating a potential integration.

I begin by introducing the simulation tool, and then present all required thermal parameters. Then I present the geometries of the switches to simulate and their specific simulation conditions. Finally I present the simulation results of the switches for different heating currents and material combinations and discuss the results.

### 3.1 Simulation tool

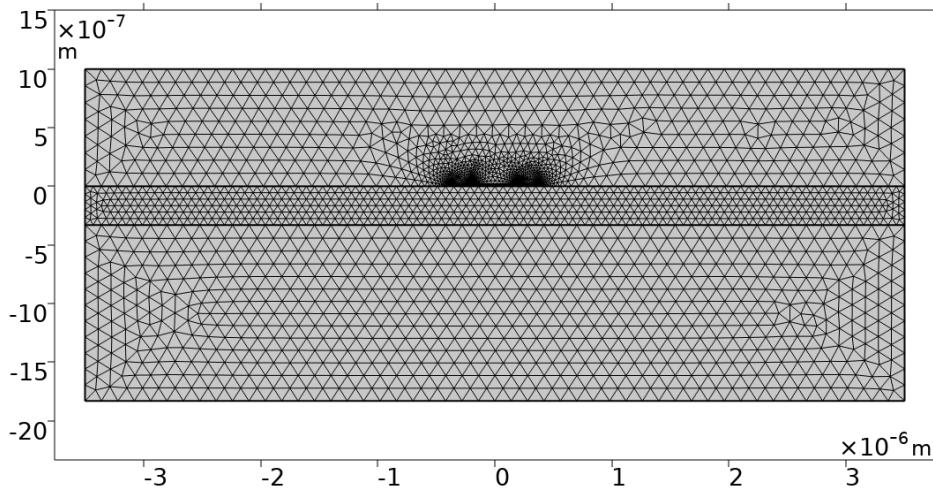

#### Comsol

I do the transient thermal simulations via COMSOL Multiphysics, a commercial physics simulation software. It allows to simulate a wide range of physical phenomena, such as electromagnetism, structural mechanics or fluid flow. I use the module for transient thermal heat transport.

The simulation is based on the finite-element-method (FEM), where differential equations governing the physical interactions are solved numerically. To this end, the desired physical problem defined by the user is discretized both in space and in time. The geometry is divided into a mesh of many small but finitely sized domains, and the desired time span is divided into small finite time steps. The differential equations are then evaluated in discrete time steps and on the discrete geometric domains, approximating the real continuous dynamics. To this end, both the step size and the spatial mesh size need to be chosen small enough such that the discretization does not introduce significant artifacts in the simulation result.

As an input, Comsol requires the thermal parameters of all involved materials. For our temperature range of interest (cryogenic temperatures in the regime 2-20K), such

Figure 3.1: A view of the 2D-Mesh employed in the simulations. Near geometries of smaller scale the mesh is automatically adapted to finer resolution, to treat the small scales appropriately

material parameters were unfortunately not readily available by any internal library. Thus, I had to collect these parameters from literature and convert them to a format amendable to Comsol.

## 3.2 Material properties at cryogenic temperatures

The materials which I want simulate can be sorted into groups, each dictated by it's own considerations:

- **Si, SiO<sub>2</sub>, LiNbO<sub>3</sub>, NbN:** The constituents of the material stack required for this chip.

- **SiN:** The default waveguide material on most chips where LiNbO<sub>3</sub> is not required. Prominent enough that I want to include it for completeness.

- **Au, Pd, Ti:** Metals that are available for deposition by the fabrication process. Useful as electrical connections, electrodes and on-chip resistors.

Some of the materials are required to be simulated because they will be part of any fabricated chip, while others are optional. The optional ones were chosen by availability of fabrication. In the case of SiN, it's simulation would not be directly necessary to this thesis, but since it is part of many other photonic designs, for which cryogenic simulations could also become interesting, I include it here in for any future reader working with SiN.

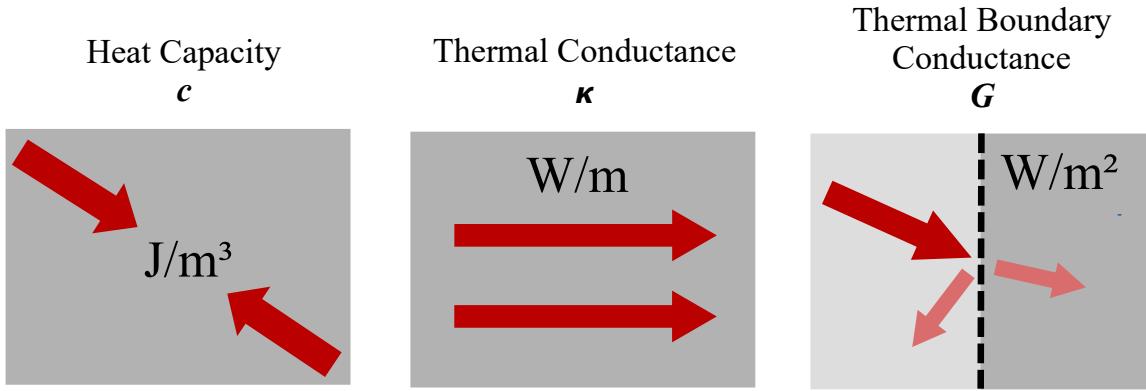

For each of these material, Comsol requires the following thermal properties

- its heat capacity  $c$

- its thermal conductivity  $\kappa$

- its thermal boundary conductivity  $G$

- its electrical resistivity  $\rho$  (for the metals and NbN)

A sketch of the physical meaning of the thermal parameters and their involved units is given in figure 3.2. While heat capacity  $c$  and thermal conductance  $\kappa$  might be familiar to most readers, thermal boundary conductance  $G$  might be not. Each parameter is now shortly introduced and its physical particularities discussed. I comment on the discovered literature results and the chosen parameters values.

Figure 3.2: The thermal properties required for simulation

## Simulation at cryogenic temperatures

Some preliminary comment on the strategies applied in the next sections:

I simulate the thermal properties of our system in the temperature range from 2 and 20K. 2K is the temperature at which our experiments will be performed, while 20K is the maximum temperature reached by the simulated heating elements given by the maximum heating current chosen for simulation.

Many of the popular and simple theoretical models that accurately describe thermal parameters in the room-temperature regime are no longer reliable at cryogenic temperatures [42]. At low temperatures, new exotic and less well studied electronic and thermal transport phenomena appear, requiring more sophisticated models. However, following and using these models to extract the thermal parameters would be beyond the scope of this thesis.

I will rely mostly on published experimental data. Multiple sources are referenced where available, giving some more statistical security to the chosen values. However, finding multiple sources was not always possible. When no direct data is available for a specific parameter, I try to derive it from the other available parameters for a given material, following the steps that are reported in literature to calculate such missing parameters.

For each extracted parameter I give the corresponding temperature range on which the parameter value is based on.

### 3.2.1 Heat capacities

Heat capacity  $c$  is given in units  $\text{J}/\text{m}^3\text{K}$  and specifies how much energy a material can absorb in a given volume before its temperature increases by 1 Kelvin. The most popular way to model heat capacities is via the Debye-T<sup>3</sup> Model [105], which assigns each material a Debye-Temperature  $\Theta_D$ , from which the heat capacity can then be calculated via the prominent formula

$$c = \frac{12\pi^4}{5} \left( \frac{T}{\theta_D} \right)^3 \quad (3.1)$$

However, for the low temperatures we are dealing with here, the Debye-Model starts to break down. To quote one paper, referencing the temperature range below 10K: "the calculated Debye specific heat is more than an order of magnitude less than the total specific heat, indicating that in this temperature range  $C$  is completely dominated by nonacoustic modes" [106].

The collected heat capacities from reported experiments in literature for every material are listed in table 3.1. It turned out that SiN and SiO were by far the most popular materials amongst our selection, providing ample data. For the metals, the electronic heat capacity must be included in tandem with the phononic contributions. This might be one of the still more widely known low-temperature phenomena [105].

Table 3.1: Heat capacities

| Material | Heat Capacity $c$                                                                                              | Range    | References*                                      |

|----------|----------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------|

| SiN      | $279 \text{ J}/\text{m}^3\text{K}^2$                                                                           | 3-10 K   | [106], [107] [108] [109]                         |

| NbN      | $1.03 \text{ J}/\text{m}^3\text{K}^4$                                                                          | 3-16 K   | [79], [110] [23]                                 |

| SiO      | $5.24 \text{ J}/\text{m}^3\text{K}^4$                                                                          | 0.1-10 K | [111], [112] [113] [106] [114] [115] [116] [117] |

| LiNbO    | $6.28 \text{ J}/\text{m}^3\text{K}^4$                                                                          | 2-20 K   | [118],[119]                                      |

| Pd       | $c_{\text{el}} = 1056 \text{ J}/\text{m}^3\text{K}^2$<br>$c_{\text{ph}} = 10.8 \text{ J}/\text{m}^3\text{K}^4$ | 2-18 K   | [120], [121]                                     |

| Ti       | $c_{\text{el}} = 320 \text{ J}/\text{m}^3\text{K}^2$<br>$c_{\text{ph}} = 2.47 \text{ J}/\text{m}^3\text{K}^4$  | 3-16 K   | [79]                                             |

For Pd and Ti:  $c = c_{\text{el}}T + c_{\text{ph}}T^3$

\*The first reference per line is the main reference for the given value, the additional references show the range of other or similar reported values

Most reported heat capacities scaled with  $\text{K}^{-1}\text{K}^{-3}$ , indicating that indeed they are dominated by some phononic contribution (even if the prefactor via the Debye-model might be off). However, for SiN in particular, ref.[106] shows explicitly that if it is layered on top of a SiO substrate its heat capacity is increased substantially in the temperature range 3-10K, compared to being layered on top of substrates. The temperature-dependent

scaling was also found to be different, in this regime SiN scaled with  $K^{-1}K^{-1}$ . Since in our wafer stack, SiN is directly on top of SiO, I choose that specific value over the others.

### A comment on the different temperature scalings $K^{-n}$

There exists a subtle difference between linearized and generalized units for heat capacities, which is also relevant to the application to Comsol, thus I want to comment on it:

In the vicinity of some fixed temperature  $T_0$ , the heat capacity of a material can be given in units  $c = J/m^3K$ , which is to be read as " $J/m^3$  heat capacity per unit change in temperature". This description is good as long as the heat capacity does not change appreciably around  $T_0$ . The units of  $c$  can thus be also called "linearized" [122]. For materials at room-temperature this is often indeed a good enough approximation. Elementary crystals for example reach the Dulong-Petit Limit of a constant of  $c \approx 3R$  (with  $R = 8.3J/molK$ ), which is independent of temperature [123].

At low temperatures, however, the heat capacity *does* change appreciably with each degree Kelvin, and in many cases with a  $T^3$  dependency [79]. A linearized description around a single temperature would be wrong, and instead a more precise notation is the following : For NbN, for example, the heat capacity should be written as  $c_{NbN} = \alpha_{NbN}T^3$ , with  $\alpha_{NbN} = 1.03 J/m^3K^4$ . For SiN, the calculation would be  $c_{SiN} = \alpha_{SiN} \cdot T$  with  $\alpha_{SiN} = 297J/m^3K^2$ . Here, the scaling factors have generalized units  $J/m^3K^n$ , where the scaling power  $n$  reflects some details about the specific physical origin of the heat capacity.

For a scaling factor  $\alpha$  with units  $K^{-n}$  the heat capacity is  $c = \alpha \cdot T^{n-1}$ . The information in table 3.1 is thus translated into Comsol by entering  $c_{Comsol} = c_{here} \cdot T^{n-1}$  as the heat capacity for each material, with it's respective scaling  $n$ . This way, the overall product provided to Comsol again has linearized units  $J/m^3K$  (as required by the software), but it's numeric value now changes dynamically during the simulation. Comsol allows to put dynamic values such as  $T$  inside material parameter definitions.

As a shorthand, I still denote the heat capacities in table 3.1 with the letter  $c$ , as this is also the common usage in most published work [106], where the translation between linearized units and generalized units, the way I have spelled it out here in detail, is implied implicitly.

### 3.2.2 Thermal conductivities

Thermal conductivity  $\kappa$  is measured in units  $W/mK$ , and specifies how well heat can propagate between two points with temperature gradient  $\Delta T = T_2 - T_1$  within a material. The explored literature data on experimentally measured thermal conductivities revealed a great variety of scaling powers: Constant values for SiO, linear T-scaling for Pd and Ti, quadratic T-scaling for SiN and bulk-LiNbO<sub>3</sub>, and cubic T-scaling for NbN and thin-film LiNbO<sub>3</sub>. For SiO in particular, the literature mentioned multiple times a "universal plateau" of constant conductivity in the range of 2-10K, which is accredited to it's amorphous structure [114].

The different temperature scalings are applied to Comsol the same way as described above for heat capacities: For every  $\kappa$  given here with units  $K^{-n}$  I entered  $\kappa T^{n-1}$  as the thermal conductance into Comsol.

Table 3.2: Thermal conductivities

| Material                  | Thermal conductivity $\kappa$       | Range  | References*                                |

|---------------------------|-------------------------------------|--------|--------------------------------------------|

| SiN                       | $8 \times 10^{-3} \text{ W/mK}^3$   | 3-20 K | [106], [124] [109] [125] [126]             |

| NbN                       | $3.4 \times 10^{-5} \text{ W/mK}^4$ | 2-10 K | [79], [127], [23]                          |

| SiO                       | $8 \times 10^{-2} \text{ W/mK}$     | 3-10 K | [114], [106] [114] [128] [129] [116] [117] |

| SiO (t.f.)                | $1.1 \times 10^{-4} \text{ W/mK}^3$ | 2-10 K | [130]                                      |

| LiNbO <sub>3</sub>        | $1.5 \text{ W/mK}^3$                | 5-10 K | [131]                                      |

| LiNbO <sub>3</sub> (t.f.) | $3.3 \times 10^{-3} \text{ W/mK}^4$ | 2-10 K | [118] +Casimir approx                      |

| Pd (t.f.)                 | $3.0 \times 10^{-1} \text{ W/mK}^2$ | 1-30 K | Via Eq. 3.3, [132] [133]                   |

| Ti (t.f.)                 | $3.2 \times 10^{-2} \text{ W/mK}^2$ | 3-16 K | Via Eq. 3.3, [79]                          |

t.f = thin film

\*The first reference per line is the main reference for the given value, the additional references show the range of other or similar reported values

## Thin layers

In very thin materials, phonons can experience additional scattering losses at the boundaries compared to bulk materials. This influence becomes significant when the thinnest dimension of the material is comparable or smaller than the mean free path of the phonons [134]. In this regime, one can make the approximation that the new mean free path of the phonons is just given by the geometric limitation, and calculate the thermal conductance via the Casimir-Limited approximation [135][134]:

$$\kappa = \frac{1}{3} v c l \quad (3.2)$$

where  $v$  is the averaged sound velocity in the material,  $c$  is the heat capacity and  $l$  is the film thickness. As one example, the mean free path of phonons in SiO at T=2K is  $\lambda = 500\text{nm}$  [106]. Any layer thinner than 500nm would thus have reduced thermal conductivity compared to published bulk values.

I follow the approach in [136] and use this Casimir-limited approximation to calculate the thermal conductivity for the 330nm thin LiNbO<sub>3</sub> layer, using for the bulk heat capacity the value reported in table 3.1 and as sound velocity the value  $v = 7\text{km/s}$  [?].

The only other thermal conductivity of LiNbO<sub>3</sub> I could find was given for a bulk crystal and is reported in [131]. Comparing these two values, the Casimir-Limited approximation gives a value by a factor 50 smaller than the bulk value for the temperature. Since this is a rather big discrepancy, this would be one of the most relevant material parameters to check in again.

## Wiedemann-Franz Law

For metals with known resistivity  $\rho$  the Wiedemann-Franz law [132] can be used to calculate the thermal conductance:

$$\kappa = L_0 T / \rho \quad (3.3)$$

where  $L_0 = 2.44 \cdot 10^{-8} \text{V}^2 \text{K}^{-2}$  is the Lorentz-constant. I use this law to calculate the thermal conductivities of Ti and Pd because I have access to their resistivity values for very thin films at cryogenic temperatures (see section 3.2.4) which fits quite well to our desired simulation situation.

### 3.2.3 Thermal boundary conductances

Thermal boundary conductance  $G$  is measured in units  $\text{W}/\text{m}^2\text{K}$  and specifies how well heat can propagate between the interface of two materials with a temperature gradient of  $\Delta T = T_2 - T_1$ . By units, it can be distinguished from thermal conductances due to its  $m^{-2}$  scaling instead of  $m^{-1}$ . The physical origin of the boundary conductance lies in a mismatch between the phononic modes of two touching materials [137]. The less similar the respective phononic modes are, the higher the probability that a phonon incident on the boundary will be reflected instead of transmitted. This results in a lower heat conductivity through the boundary.

One way to model the phononic mismatch between two materials is given by the Diffusive mismatch model (DMM) [138]. I follow here closely the treatment by Dane et al. [135] from Berggrens Group, since their work is directly concerned with modeling SNSPDs and similar thin film superconducting devices at cryogenic temperatures, providing an excellent fit for our desired application. Further details on the thermal modeling of specifically NbN and similar materials can also be found in the thesis by Dane [122].

Given two materials, their thermal boundary conductance in the DMM model can be expressed via the Kapitzka cooling rate  $\Sigma_K$  [139], which is given by

$$\Sigma_K = \frac{\pi^2 k_B^4}{120 \hbar^3} \cdot \frac{[1/v_{1L}^2 + 2/v_{1T}^2] \cdot [1/v_{2L}^2 + 2/v_{2T}^2]}{[1/v_{1L}^2 + 2/v_{1T}^2 + 1/v_{2L}^2 + 2/v_{2T}^2]} \quad (3.4)$$

where  $v_{iL}$  and  $v_{iT}$  are the longitudinal and transversal speed of sounds of the two materials.

If two interfacing materials have different temperatures  $T_1$  and  $T_2$ , the heat transfer  $P_{12}$  from the hot to the cold material can then be calculated via the black-body phonon assumption [122] [135] via

$$\frac{P_{12}}{A} = \Sigma_K (T_1^4 - T_2^4) \quad (3.5)$$

where  $A$  is the contact area between the materials. For small temperature-differences  $\Delta T$ , the black body scaling can be linearized around a single temperature [136]. Note that an extra factor 4 appears due to this linearization.

$$(T_1^4 - T_2^4) \approx 4T^3 \Delta T \quad (3.6)$$

The heat transfer can then also be expressed in this linearized form

$$\frac{P_{12}}{A} \approx 4\Sigma_K T^3 (T_1 - T_2) \quad (3.7)$$

Now for comparison, in Comsol heat transfer between boundaries is treated with the following equation

$$\frac{P_{12}}{A} = h_{12}(T_1 - T_2) \quad (3.8)$$

We see that to translate between the Kapitzka-Model and Comsol, one needs to do the following identification:

$$\Rightarrow h_{COMSOL} = G_{12}T^3 = 4\Sigma_K T^3 \quad (3.9)$$

where I introduced the intermediate notation  $G_{12} = 4\Sigma_K$ , following [79] and [139]. When combining values from literature, one needs to take there of whether, and where, this prefactor of 4 might be hidden.

I use the Kapitzka-Equation 3.4 and sound velocities from [136] to calculate the thermal boundary conductance parameter  $\Sigma_K$  for every pairwise combination of our materials of interest (excluding NbN, see next paragraph), multiply by four to translate into the format  $G_{12} = 4\Sigma_K$ , and report these values in table 3.3. Note that again, I enter the values into Comsol as  $G_{12}T^3$  to have correct units and correct temperature scaling.

Thermal boundary values for NbN I took as  $\Sigma_K$  directly from [135], marked in bold font in table 3.3, since those were calculated with the more involved acoustic mismatch model (AMM) and reported to match even better with experiments. For the rest of the pairs I had to resort to own calculations. A full overview on the topic of thermal boundary conductance can be found in [137], a more modern review in [138]. Experimentally, its has also been tried to extract cryogenic thermal boundary parameters using superconducting nanowires as thermals sensors [140].

Table 3.3: Thermal Boundary Conductances. Normal font: Calculated via eq. 3.4. Bold font: Retrieved from [136]. Mind the factor 4 in the definition of  $G_{12}$  (eq. 3.9)

| $G_{12}$ [W/m <sup>2</sup> K <sup>4</sup> ] | Si         | SiO        | SiN        | LiNbO <sub>3</sub> | NbN |

|---------------------------------------------|------------|------------|------------|--------------------|-----|

| Si                                          | -          | -          | -          | -                  | -   |

| SiO                                         | 538        | -          | -          | -                  | -   |

| SiN                                         | 359        | 441        | -          | -                  | -   |

| LiNbO <sub>3</sub>                          | 559        | 785        | 455        | -                  | -   |

| NbN                                         | <b>532</b> | <b>656</b> | <b>484</b> | <b>824</b>         | -   |

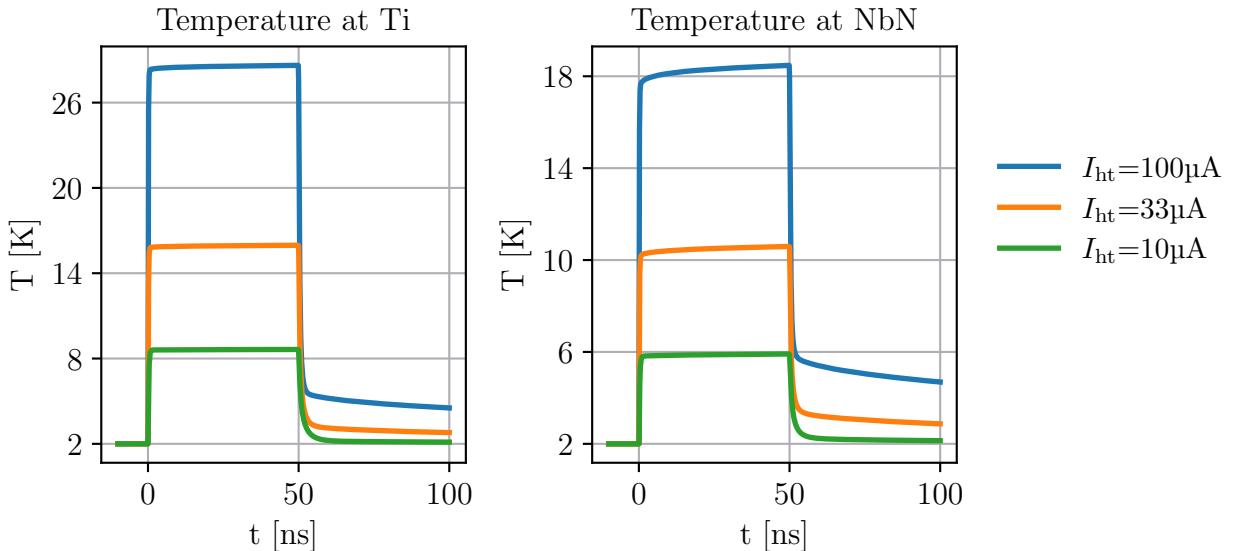

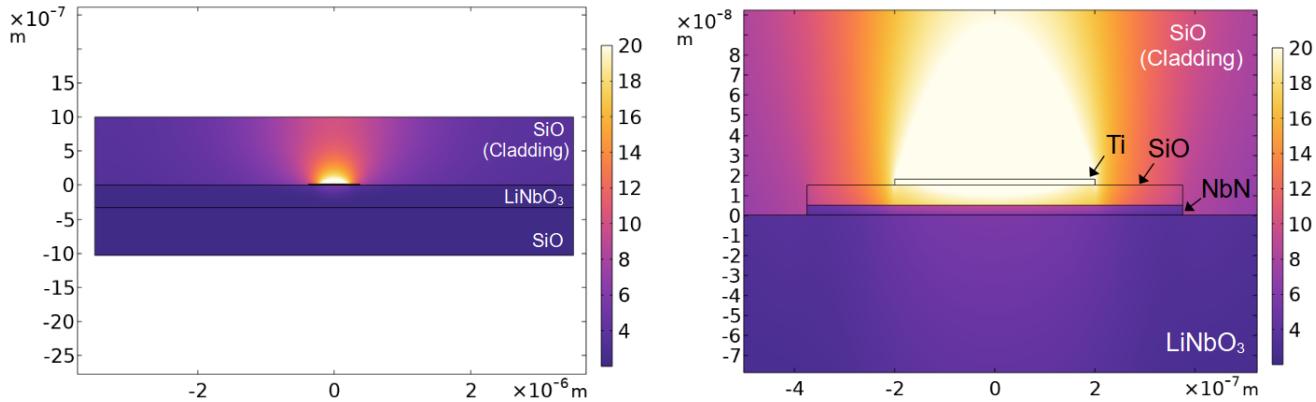

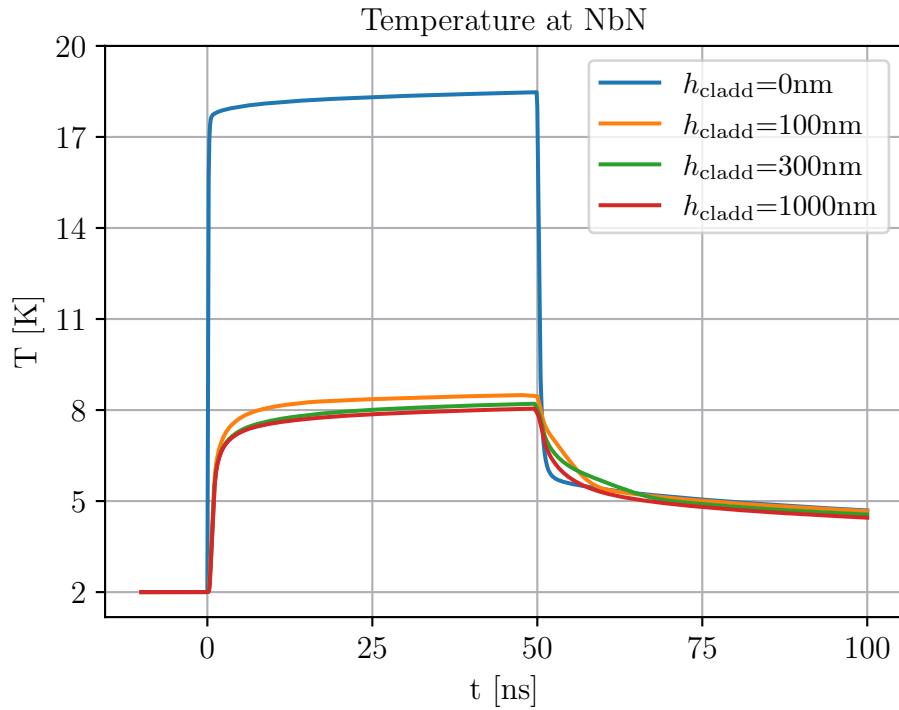

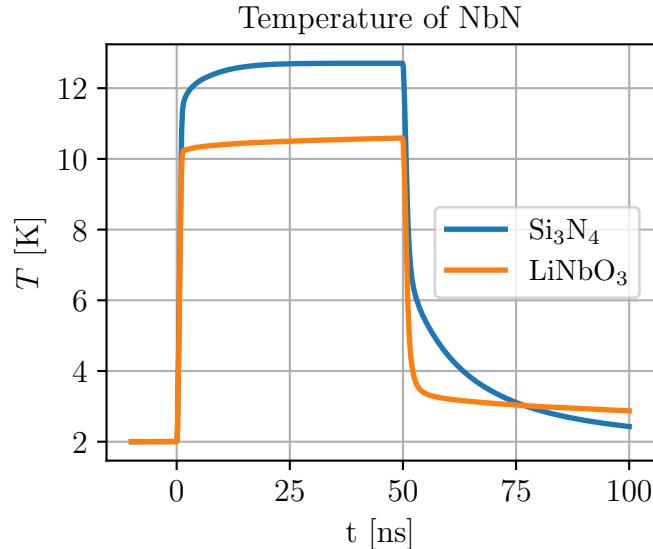

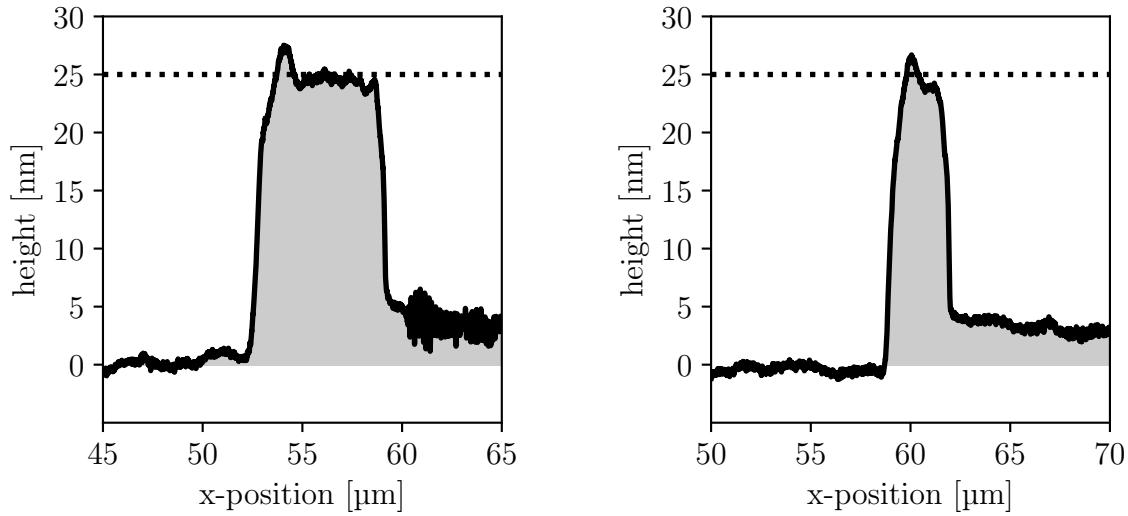

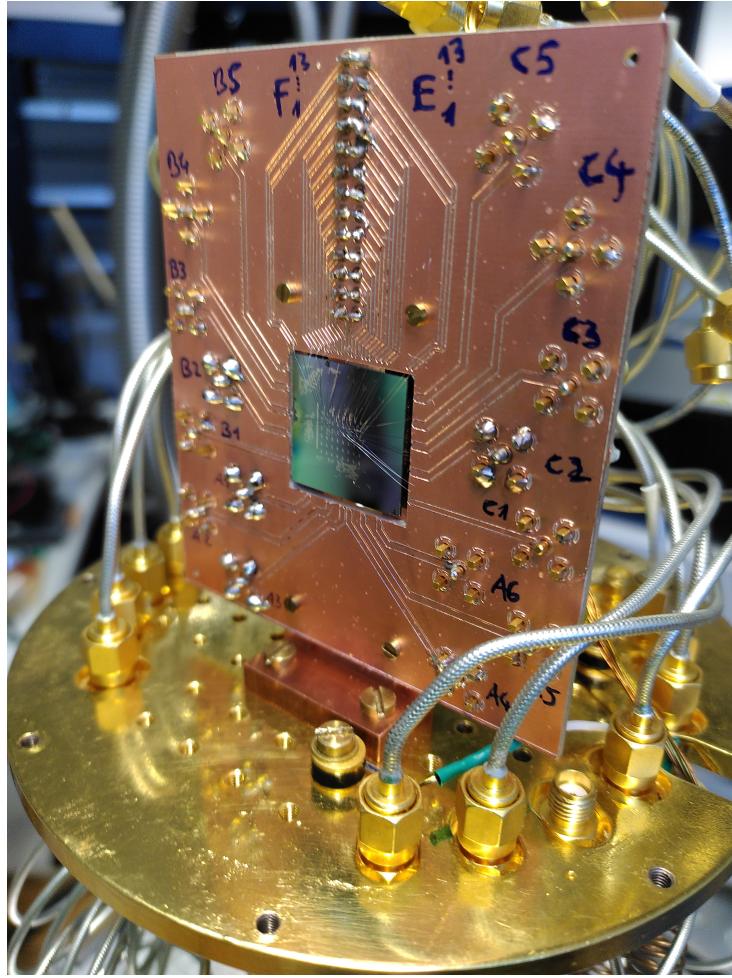

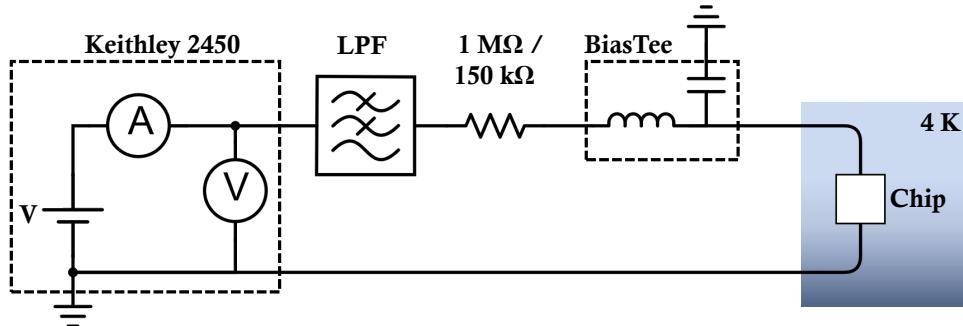

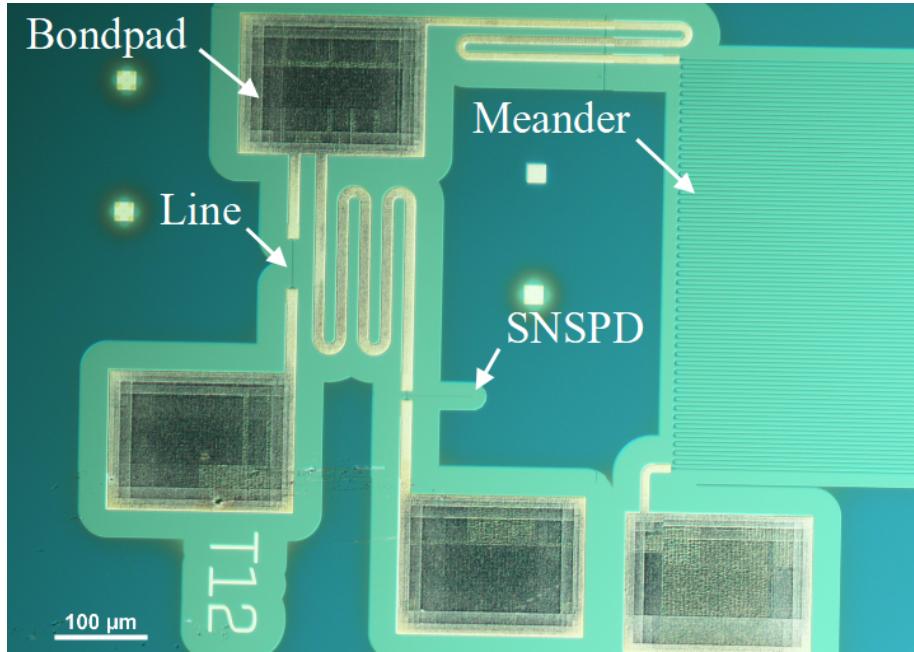

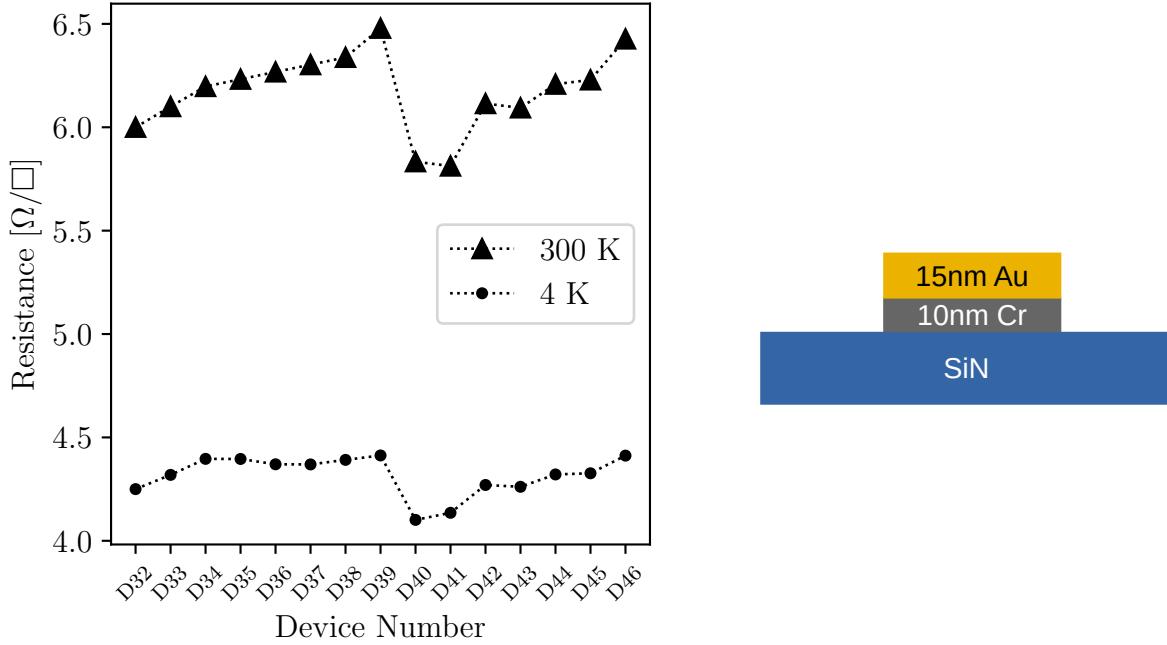

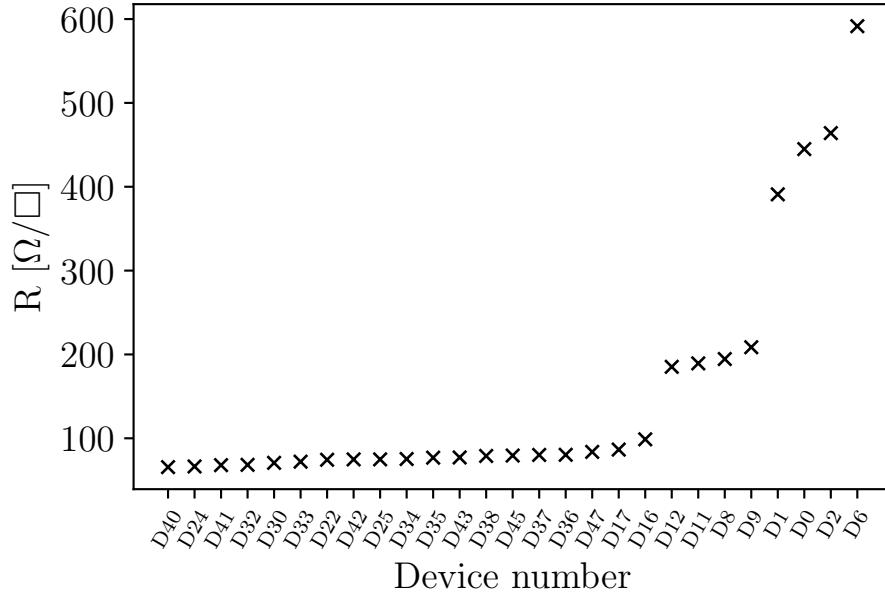

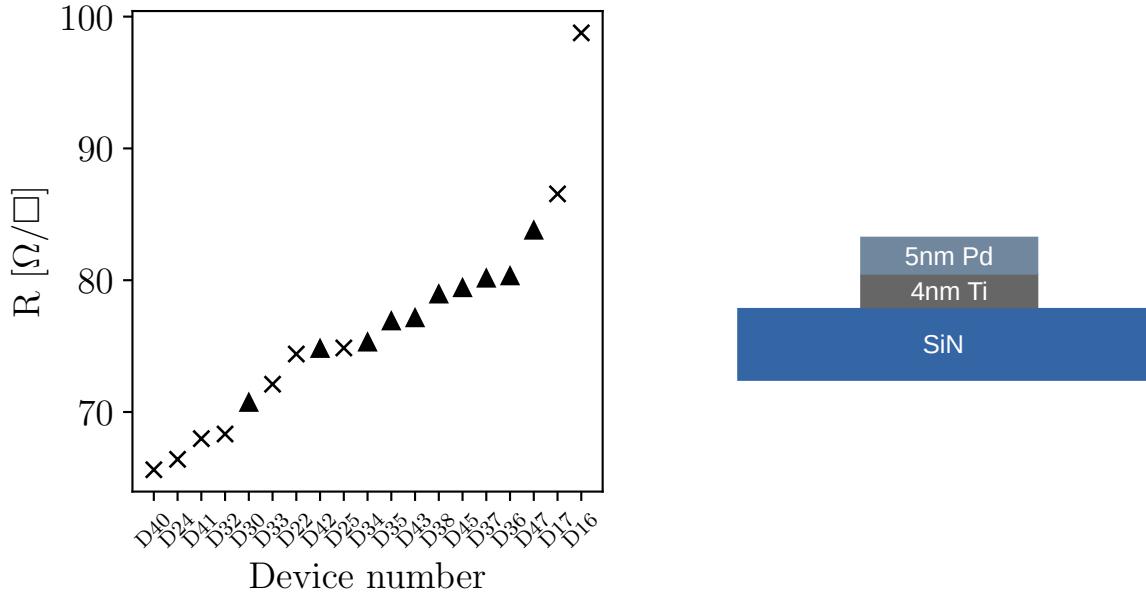

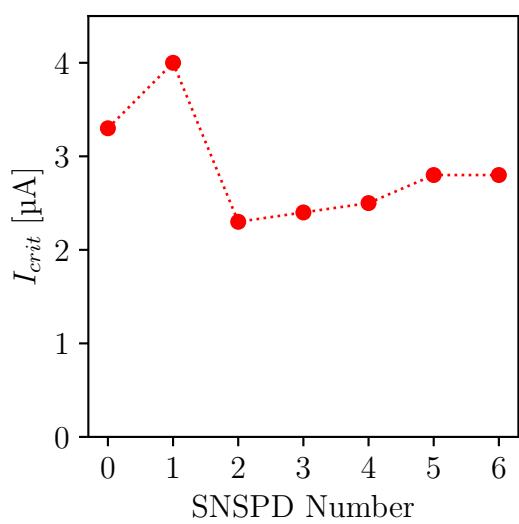

| Ti                                          | 624        | 917        | 496        | 981                | 694 |